YM3802アプリケーションマニュアル CATALOG No.: LSI-2438022 1987.9

Scanned by HansO, 2005, original supplied by Jetze Mellema

# **TABLE OF CONTENTS**

| Cł | napter | r                                           | Page |

|----|--------|---------------------------------------------|------|

| 1. | Intr   | roduction                                   | . 1  |

|    | 1.1    | General                                     | . 1  |

|    | 1.2    | Features                                    | . 2  |

|    | 1.3    | Terminology                                 | . 4  |

|    |        |                                             |      |

| 2. | Sim    | plified description of functions            | . 6  |

|    | 2.1    | Pin assignment.                             | . 6  |

|    | 2.2    | Internal block functions                    | . 9  |

|    | 2.3    |                                             |      |

|    |        |                                             |      |

| 3. | Con    | nmunication functions                       | . 17 |

|    | 3.1    | Serial communication                        | . 17 |

|    | 3.2    | Cassette tape interface (FSK modulation)    | . 24 |

|    | 3.3    | Functions related to transmission           | . 31 |

|    | 3.4    | Functions related to reception              |      |

|    |        |                                             |      |

| 4. | MID    | I service functions                         | . 40 |

|    | 4.1    | MIDI clock controller and related functions | . 40 |

|    | 4.2    | Sequencer                                   | . 48 |

|    | 4.3    | SYNC controller and CLICK counter           |      |

|    | 4.4    | Address hunter                              | . 56 |

|    | 4.5    | Utilization for other than MIDI services    | . 60 |

|    |        |                                             |      |

| 5. | Othe   | er functions                                | . 61 |

|    | 5.1    | General-purpose timer                       |      |

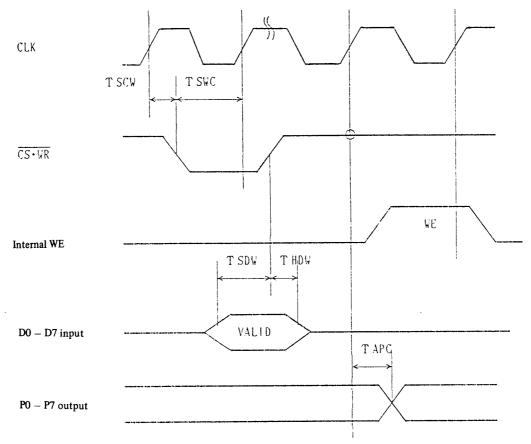

|    | 5.2    | I/O controller                              | . 63 |

|    |        | IRQ controller.                             |      |

|    |        | System control                              |      |

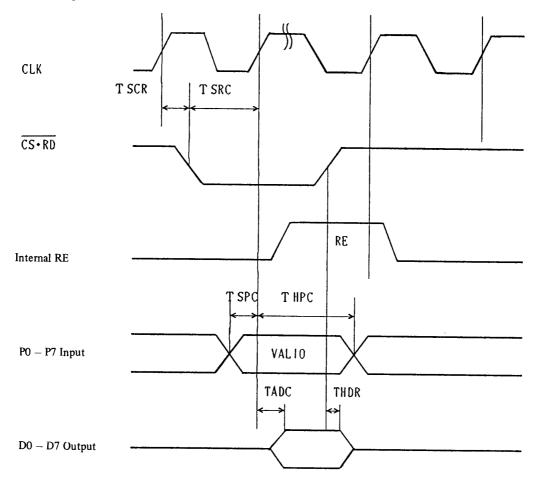

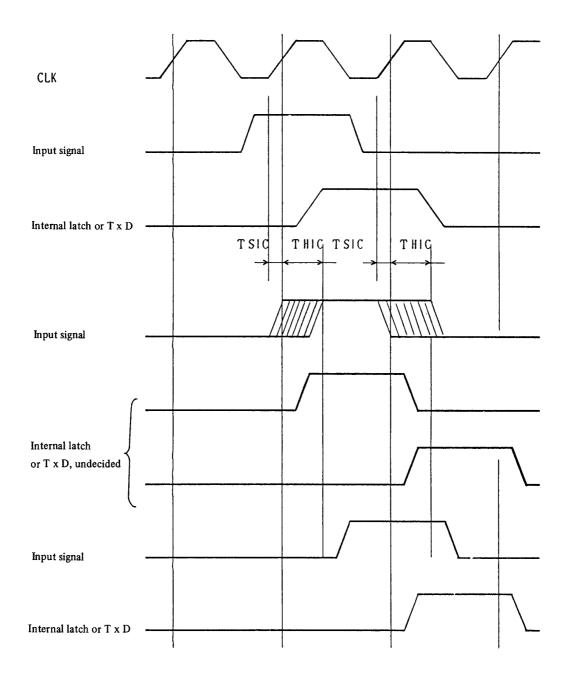

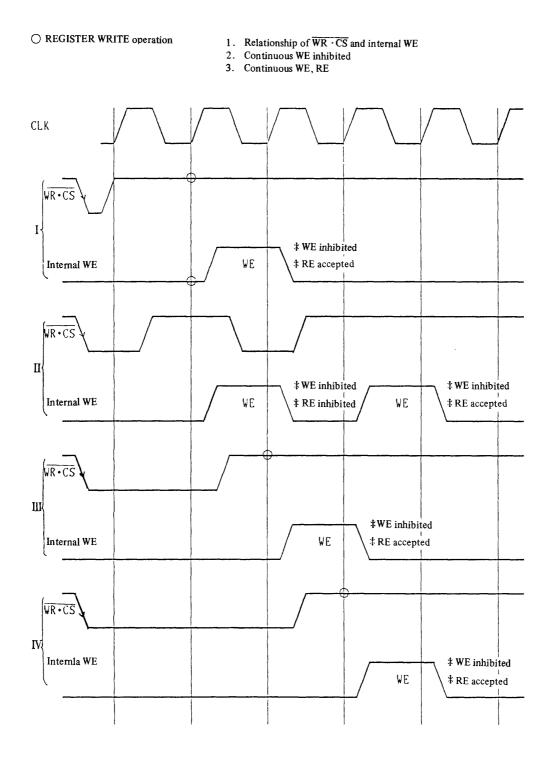

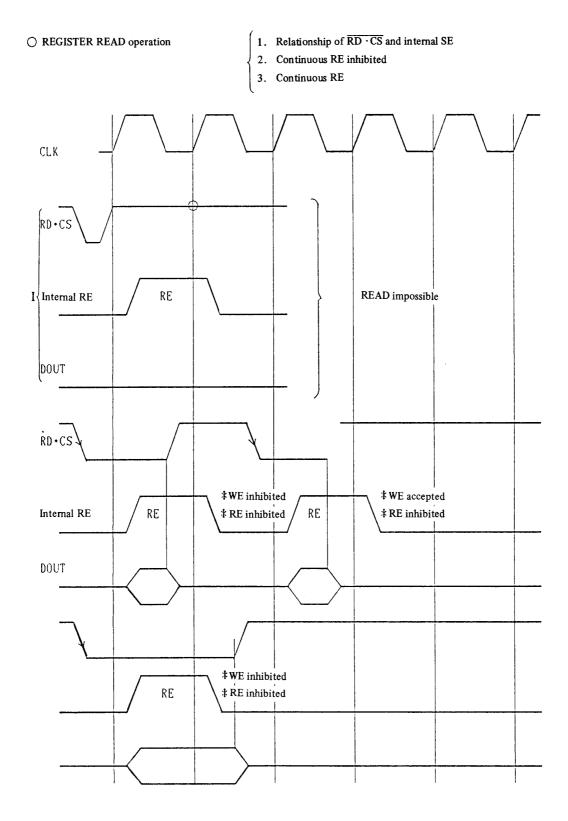

| 6. | Inte | faces                      | 3 |

|----|------|----------------------------|---|

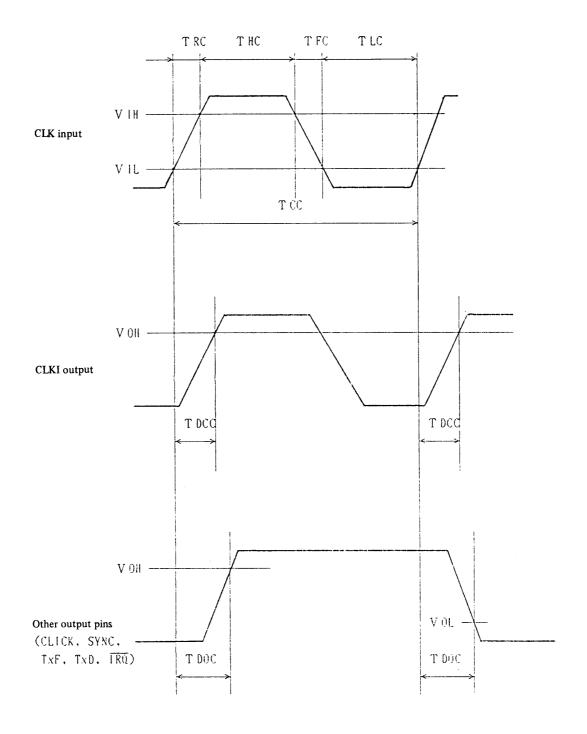

|    | 6.1  | Clock interface            | 3 |

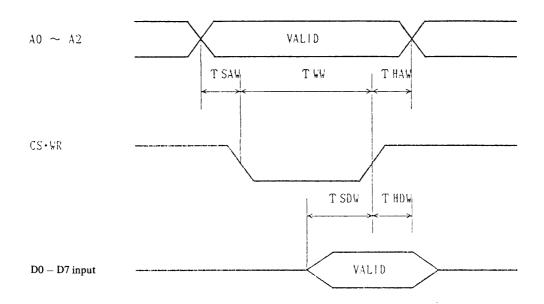

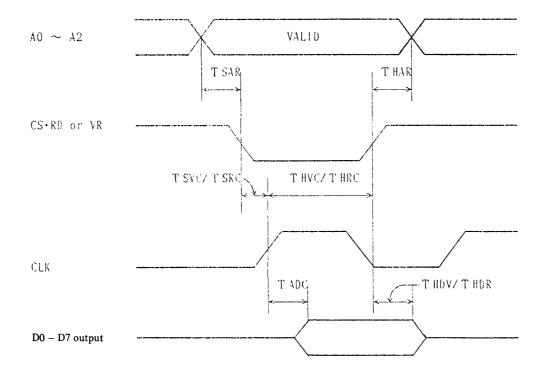

|    | 6.2  | CPU interface              | 4 |

|    | 6.3  | Transmit/receive interface | 5 |

|    |      |                            |   |

| 7. | Elec | trical characteristics     | 6 |

| Appendixes - | Α. | Pin assignment                          |

|--------------|----|-----------------------------------------|

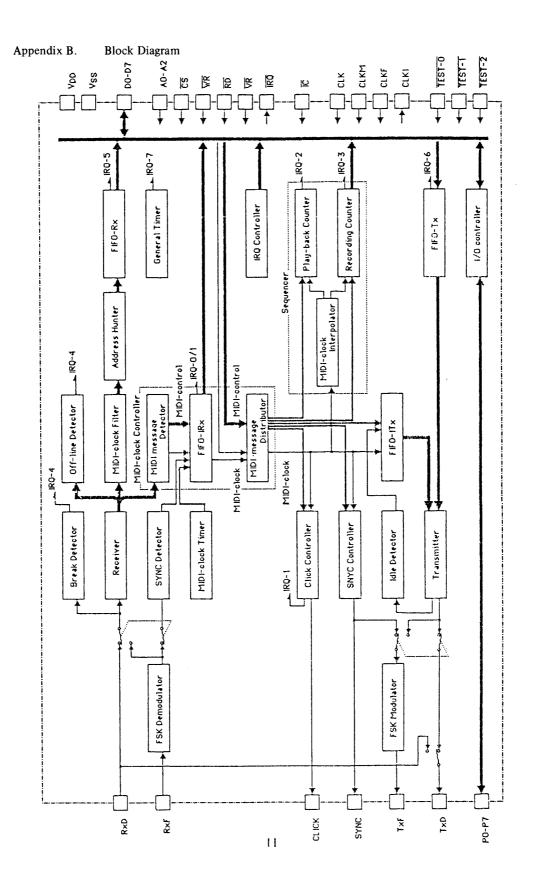

|              | B. | Block diagram II                        |

|              | C. | Register map III                        |

|              | D. | Table of register functions IV          |

|              | Ε. | Table of IRQ setting/clearing status IX |

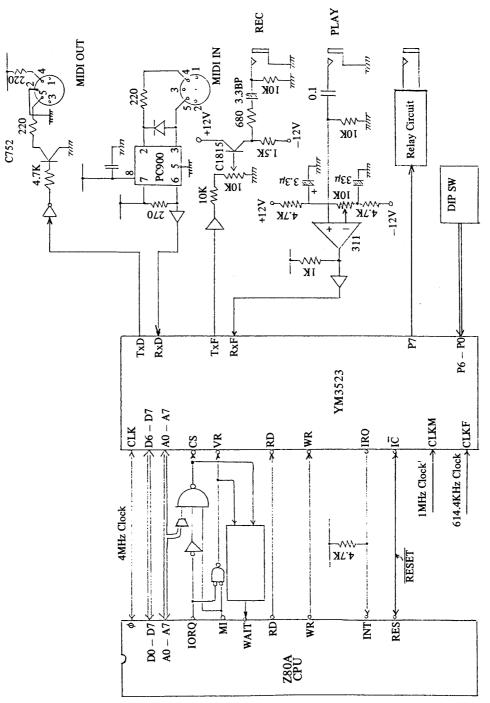

|              | F. | Circuit example(s). XI                  |

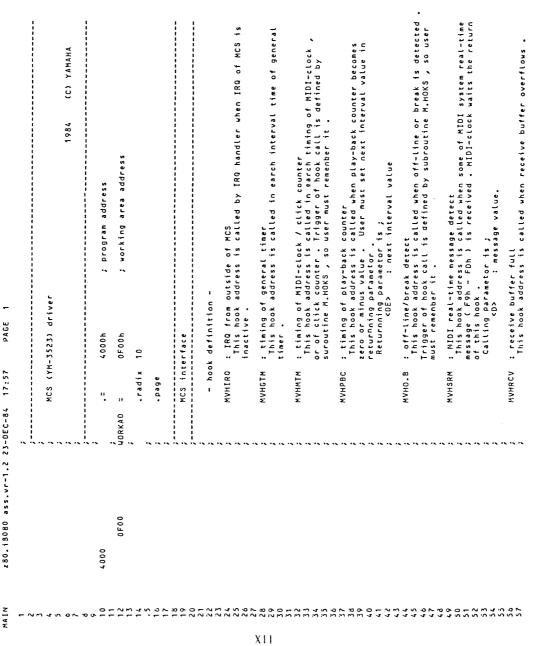

|              | G. | Sample program                          |

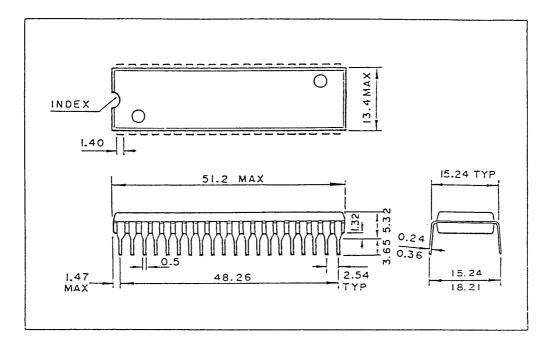

|              | H. | Package outline                         |

# 1. INTRODUCTION

### 1.1 General

The YM3523 is an LSI device featuring an asynchronous serial communication interface, a frequency divider that acts a communication rate generator, an interface for the cassette tape recorder, transmit/receive data buffers, timers, counters and a parallel input/output port. With this LSI a part of the MIDI data processing can be performed by hardware.

The YM3523 LSI has two output pins and three counters that synchronize with the MIDI clock and the tape SYNC can be easily realized. The MIDI clock is generated by the MIDI clock timer, the tape SYNC signal or the clock message contained in the received serial data. Another way of the generation of the MIDI clock is a process with the host CPU control. This LSI has the priority transmission and reception capability of the MIDI system real-time message over other messages and also can support the processing of the system exclusive message.

1

Each of the MIDI counters can be utilized as general-purpose timer/counter.

### 1.2 Features

- Serial communication

- 7- or 8-bits ..... Character,

- 1- or 2-bits ..... Stop bit,

- 1- or 4-bits ..... Parity bit,

- Start bit error detection,

Automatic break detection and break character generation,

- Character length, Types of parity and stop bits and communication rate are selectable for transmission and reception separately.

- Cassette tape recorder interface

One wave/two wave FSK modulation,

Automatic follow-up function for polarity and phase,

Transfer-rate check function,

Used for ordinary serial communication or cassette tape recorder interface in transmission and reception (separately).

• Communication rate generater

Communication rate generation of  $75 \sim 19200$  bps and 31.25K bps.

Reception is performed at the internal clock rate that is 16 times the communication rate.

Communication rates of DC through 125K bps can be obtained by selecting the frequency of a communication rate generating clock.

- General-purpose 8-bit parallel input/output port.

- General-purpose 14-bits timer.

- 128 bytes FIFO buffer for reception and 16 bytes FIFO buffer for transmission.

- MIDI support functions

SYNC out, CLOCK out; output of a pulse signal synchronized to the system real-time message.

Automatic transmitting function, priority transmitting function and priority receiving function (without involving the receiving FIFO buffer) of the system real-time message.

8- and 15-bit counters for counting the interpolated, high-accuracy signal of the MIDI clock.

Special 14-bit timer for determining MIDI clock generation timing. Detecting function of the MIDI clock from the received serial data.

Tape SYNC function.

Automatic output of the tape SYNC signal

Active sense function

ID code check function for the system exclusive message.

- Vector output function according to 8-level interrupt factors

- C-MOS, 3µ rule, 4MHz maximum system clock, 10mA power consumption

- Single 5V power supply, TTL level interface

- 40-pin plastic DIP package

# 1.3 Descriptions of terms

• MIDI

Abbreviation for Musical Instrument Digital Interface, a communication standard for interconnecting the synthesizer, sequencer, rhythm machine and computer. Established in 1983 among the musical instrument industry.

Operation and SYNC information on instruments, etc., can be transmitted real-time at a communication rate of 31.25K bps by the asynchronous serial communication using a 10-bit word comprising a start bit, eight data bits and a stop bit.

• Message

A communication unit of data for MIDI. One message is composed of one character of status byte and data byte whose length is status byte-dependent. The MSB of the status byte is 1 and that of the data byte is 0.

• System real-time message

A classification of the MIDI message. A general term indicating 8 types of status bytes from (F8)h to (FF)h with no data byte included. To provide a higher degree of real-time processing these messages can be transmitted by interrupting other message's data byte. The meanings of these messages are as follows:

| (F8)h | Timing Clock:   | SYNC clock. Indicates the note value of the ninety-sixth note (equivalent to $1/24$ th of the length of the quarter note). Hereafter called the MIDI clock. |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (50)  |                 |                                                                                                                                                             |

| (F9)h |                 | Undecided                                                                                                                                                   |

| (FA)h | Start:          | Start command for sequencer, etc.                                                                                                                           |

|       |                 | Starts from the opening of music.                                                                                                                           |

| (FB)h | Continue:       | Continuous start command for sequencer, etc.                                                                                                                |

| (FC)h | Stop:           | Stop command for sequencer, etc.                                                                                                                            |

| (FD)h |                 | Undecided                                                                                                                                                   |

| (FE)h | Active Sensing: | Message indicating the transmitter and transmission line                                                                                                    |

|       |                 | are operating normally.                                                                                                                                     |

| (FF)h | System Reset    |                                                                                                                                                             |

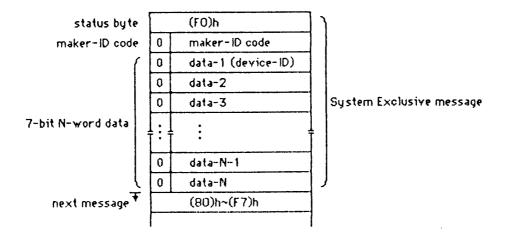

System exclusive message

One of the MIDI messages.

Large data such as instrument tone parameters and nonstandard data are transferred with this message.

Consists of status byte (F0)h and variable-length data byte. The first data byte is used as the ID code of a manufacturer. Thus the MIDI instrument manufacturer must have its ID code registered with the International MIDI standard committee. The format from the second data byte on can be decided by each manufacturer; a system exclusive message not in accordance with the manufacturer ID code can be neglected.

# • Active sense message

One of the MIDI system real-time messages. Its status byte is (FE)h. The MIDI specification requires that a transmitter transmit any message at least once per 300msec. If there is no message to be transmitted, this active sense message must be sent. When a receiver does not receive any message from a transmitter for 300msec, the transmitter or its transmission line is considered to be abnormal. In this case the sound generation is stopped and the receiver resumes its own operation.

The receiver continues its own operation until it receives the first active sense message.

### • FSK modulation

FSK is an abbreviation for frequency-shift keying, a form of digital signal recording on a magnetic (cassette) tape in which the 1 and 0 are represented by two distinct frequencies.

In the YM3523 the mark (H level = 1) and space (L level = 0) of the usual asynchronous serial signal are modulated with a frequency of two times the communication rate and a frequency equal to this rate, respectively. Demodulation function is also provided.

With this type of modulation interface to the magnetic tape is obtained. The definition mentioned above is used throughout this manual.

### • Tape SYNC

Synchronizing multiple recording or automatic performance according to the SYNC signal recorded on a magnetic tape, etc.

### • TCLK, TCLKM and TCLKF

One-cycle time of the clock signal being input to terminals CLK, CLKM and CLKF, respectively.

# 2. SIMPLIFIED DESCRIPTION OF FUNCTIONS

# 2.1 Pin assignment

The pin configuration is shown in Fig. 2.1.

• IC ... Input

The YM3523 is reset by the L level input signal to this terminal. The reset pulse width must be more than 32 clocks of the system clock to the CLK terminal (32 TCLK).

The same reset operation can be made by the host CPU operation on the internal registers of YM-3523.

• CLK ... Input

System clock input terminal

The internal operation of the YM3523, input signal sampling and output signal changing are all performed in synchronization with the internal timing clock made by this system clock. The clock rate must be more than 32 times the communication rate used. In the case of an MIDI communication rate of 31.25K bps at least a 1MHz clock rate is necessary. The maximum rate is 4MHz.

# • CLKI ... Output

Internal timing clock output terminal.

• CLKM ... Input

Input terminal for a clock that generates an MIDI communication rate of 31.25K bps (baud). Usually 1MHz or 0.5MHz is input, and 1/16 or 1/32 of this can be used as the communication rate.

This clock signal is divided to obtain a count clock for the general-purpose timer and the MIDI clock timer and also for the output pulse width at the SYNC and CLICK terminals. A divide-by-two circuit is included so that the same setting time can be obtained, irrespective of the input signal to the CLKM terminal (1MHz or 0.5MHz).

CLKF ... Input

Input terminal for a clock that generates a communication rate of  $75 \times 2^n$  series.

Usually 614.4KHz is input and communication rates from 1/8192nd of this frequency (75 bps) to 1/32nd of the same frequency (19200 bps) can be used. Can be used also for counting in the MIDI active sense function.

|        | <u></u> |    |           |

|--------|---------|----|-----------|

| VDD    |         | 40 | CLK       |

| R×D    | 2       | 39 | CLKI      |

| R×F    | з       | 38 | TEST-2    |

| CLKM   | 4       | 37 | ĪĈ        |

| CLKF   | 5       | 36 | ĪRO       |

| TxD    | 6       | 35 | VR        |

| T×F    | 7       | 34 | RD        |

| SYNC   | 8       | 33 | <b>WR</b> |

| CLICK  | g       | 32 | <u>CS</u> |

| TEST-0 | 10      | 31 | A2        |

| TEST-1 | 11      | 30 | A1        |

| P7     | 12      | 29 | AO        |

| P6     | 13      | 28 | D7        |

| P5     | 14      | 27 | D6        |

| P4     | 15      | 26 | D5        |

| P3     | 16      | 25 | D4        |

| P2     | 17      | 24 | D3        |

| P1     | 18      | 23 | D2        |

| P0     | 19      | 22 | D1        |

| Yss    | 20      | 21 | DO        |

Figure 2.1 Pin assignment

7

•  $D0 \sim D7 \dots$  Input/Output

| A0 ~ A2                | <br>Input |

|------------------------|-----------|

| $\overline{\text{CS}}$ | <br>Input |

| WR                     | <br>Input |

| RD                     | <br>Input |

| VR                     | <br>Input |

| ĪRQ                    | <br>Input |

|                        |           |

These terminals are used to provide interface to the host CPU.

- TEST-0 ~ TEST-2 ... Input Terminals used for testing the LSI. Thus, no connections are generally made.

- RxD... Input Serial data input terminal

- TxD ... Output Serial data output terminal

- RxF ... Input

Audio signal input terminal from the magnetic tape such as a cassette tape. FSK-modulated serial data are input to this terminal at the TTL level.

• TxF ... Output

Audio signal output terminal to the magnetic tape such as a cassette tape. FSK-modulated serial data are output from this terminal at the TTL level.

• SYNC ... Output

A 2msec width pulse is output from this terminal in synchronization with the MIDI clock. Used as a SYNC signal for other hardware.

• CLICK ... Output

A 2msec width pulse is output from this terminal in synchronization with the MIDI clock divided. Used when a metronome, etc., which is synchronized with the MIDI, is configured.

•  $P0 \sim P7$  ... Input/output

General-purpose I/O port with which the input/output direction of each bit can be separately set.

### 2.2 Internal block functions

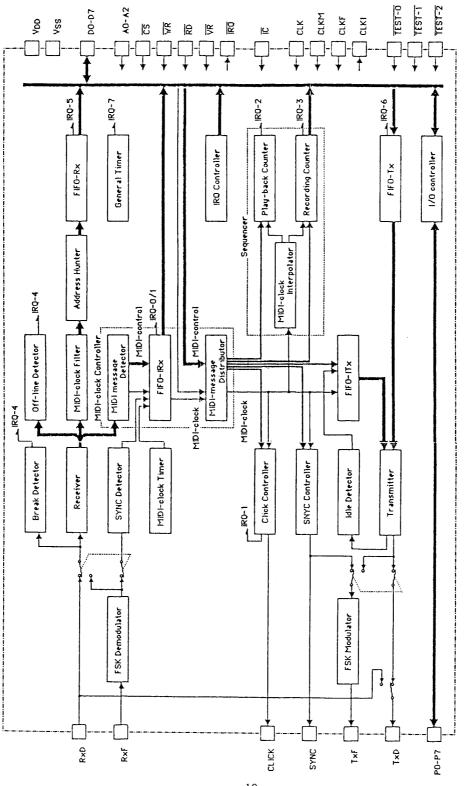

The block diagram is given in Fig. 2.2.

Transmitter

Receives data from the FIFO-ITx or FIFO-Tx. Appropriate start, parity and stop bits are added to the received data, which is then converted to serial data. This serial data is sent direct to the TxD terminal, or FSK-modulated and sent to the TxF terminal.

Communication rate, data length, type of parity bit and type of stop bit can each be set independent of the receiver, has the function of forcibly lowering the output to the break level (L level).

#### FIFO-Tx

16-byte transmitting data buffer. General serial data transmission is made by setting the data in this buffer. Because of the FIFO method the arbitrarily-set data is processed by the transmitter in the same order that it was set. An interrupt signal is generated when all the data stored in the buffer are sent to the transmitter.

Whether or not the data set area is available in the buffer can be checked from the host CPU.

#### FSK modulator

The transmitter serial data output is FSK-modulated. Its conversion rate is dependent upon the communication rate.

If the serial data is sent to the TxD terminal, the SYNC terminal output signal is FSKmodulated at a transfer rate of 1200 bps, which is then sent to the TxF terminal. The modulation execution and halt can be controlled from the host CPU.

Receiver

The serial data sent from the RxD terminal or the FSK demodulator is converted to the parallel data, and the parity and stop bits are checked. Usually, the parallel data and the error status are set in the FIFO-Rx.

Communication rate, data length, type of parity bit and type of stop bit can be set independent of the transmitter.

### FIFO-Rx

128-byte receiving data buffer. Usually, the data received by the receiver is set in the order it was received. This data can be read out anytime from the host CPU. The MIDI clock filter and the address hunter can prevent unnecessary data from being set in the FIFO-Rx. In addition to the 128 bytes for data storage the parity and stop bit check results are also stored for each data, therefore, this FIFO-Rx is in practice of the 10 bits x 128 words of storage buffer.

An interrupt signal is generated after the receiver has received one-character data and set it in the empty buffer. The overrun error flag is set when new data is set in the buffer already full of data, permitting checking from the host CPU.

# • FSK demodulator

The FSK-modulated signal input to the RxF terminal is demodulated and sent to the receiver in the form of usual serial signal. In this case the conversion rate is in accordance with the receiver communication rate. The sampling timing of the serial signal that follows the input signal fluctuation with time is sent to the receiver where the serial-to-parallel conversion is performed at this timing.

If the receiver handles the input signal at the RxD terminal this signal is demodulated at a transfer rate of 1200 bps and then sent to the SYNC detector. If the polarity accords, then the phase adjustment is performed at the time when the one wave-modulated data (L level) is demodulated. The positive or negative polarity is selectable.

Also, automatic polarity follow-up can be performed by the polarity detector circuit. The baud check circuit is included and the result can be checked from the host CPU. Since the level of the input signal at the RxF terminal can be directly checked from the host CPU, it is possible that only the adjustments of baud, polarity and phase are conducted by the software, then the demodulator output is utilized.

Break detector

Break status detector circuit for the input signal to the receiver.

If the L-level input continues during the transfer period of two characters that conform with the communication rate, data length, parity bit and stop bit set by the receiver, it is regarded as a break condition and thus an interrupt signal is issued.

• FIFO-ITx

4-byte transmitting buffer used exclusively for the MIDI system real-time message.

If data is set in the FIFO-ITx, the transmitter will transmit this data, irrespective of whether the FIFO-Tx data is present or not.

Idle detector and off-line detector

Functional blocks for the processing of the MIDI active sense.

The idle detector measures the interval between the serial data transmissions by the transmitter, and if there is no transmission for a period of 80msec the MIDI active sense message is set in the FIFO-ITx.

The off-line detector measures the interval between the receiver's serial data reception and the parallel data output. If there is no reception for a period of 300msec an interrupt signal is generated.

MIDI clock filter

With this filter the MIDI clock message (F8)h is prevented from being transferred to the FIFO-Rx. This can reduce the host CPU access to the receiving data buffer, if the reception of the clock message is used by the IRQ, etc.

• Address hunter

When the MIDI system exclusive message is received, the manufacturer ID code or the manufacturer ID code plus one-byte ID code are checked against the ID code(s) pre-stored in the register. If there is no accord, this filter (address hunter) prevents the message from being transferred to the FIFO-Rx.

# • SYNC detector and MIDI clock timer

Internal MIDI clock generation sources.

The MIDI clock timer is a 14-bit programmable interval timer. The same type of timer is used as the general-purpose timer (described later). The MIDI clock timer generates the MIDI clock timing signal instead of interrupt signals.

The SYNC detector also generates the MIDI clock timing signal on the rising edge of the signal obtained by demodulating the tape SYNC signal that is input to the RxF terminal.

In addition, the MIDI message detector (see later) generates the MIDI clock timing signal when it detects the reception of the MIDI clock message (F8)h by the receiver. The host CPU can also directly provide this timing signal.

According to this timing, concurrent operation of several functional blocks within the YM3523 can be made.

SYNC controller

Controls the SYNC signal output.

A 2msec width pulse is sent to the SYNC terminal in accordance with the internal MIDI clock. Also, the FSK-modulated SYNC output signal is sent to the TxF terminal which is recorded on a magnetic tape for use as the SYNC signal for tape SYNC operation.

CLICK counter

7-bit programmable counter to count the internal MIDI clocks.

This counter can be used as a general-purpose interval timer if the MIDI clock timer is employed as the MIDI clock generation source. When the values set in the register have been counted, a 2msec width pulse is sent to the CLICK terminal and at the same time an interrupt signal is issued. Count operation restarts by the automatic load of the counter with the preset value.

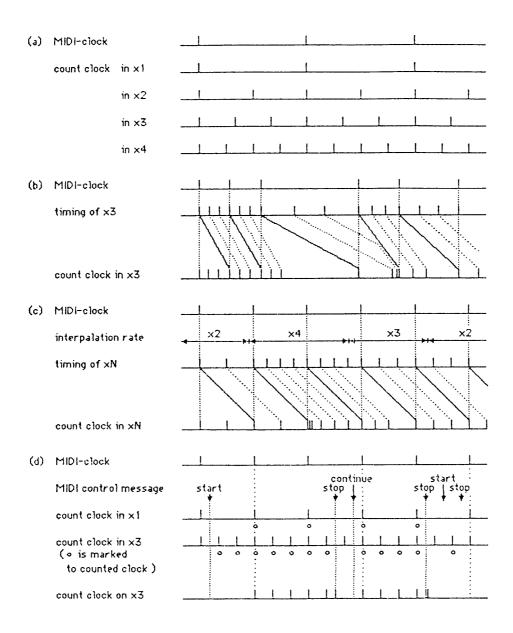

• Sequence–MIDI clock interpolator, Recording counter and Playback counter

Functional blocks for time management based upon the internal MIDI clock.

The MIDI clock interpolator generates count clocks at an interval equal to 1/nth of the MIDI clock generation interval. This provision is used to advantage when application requiring higher clock resolution is encountered.

The recording counter is an 8-bit readable fixed counter which generates an interrupt when the count reaches zero. This counter is usable as a real-time clock with its carry operation processed by the host CPU software.

The playback counter is a 15-bit programmable subtractive counter which counts the MIDI clock interpolator-generated count clocks and issues an interrupt signal when the count reaches zero or becomes negative.

Although no automatic counter initialization is performed, the addition to the present count value is possible to cope with the host CPU's counter resetting delay.

If the MIDI clock timer is used as the MIDI clock generation source, these counters can be utilized for general purposes.

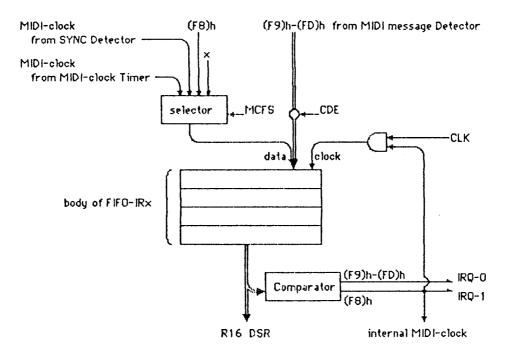

# MIDI clock controller-MIDI message detector, FIFO-IRx and MIDI message distributor Control blocks for the internal MIDI clock.

The MIDI message detector is a functional block that detects the reception of the MIDI system real-time message character by the receiver. When the reception of the clock message (F8)h is detected by the receiver this detector generates the internal MIDI clock timing signal. Similarly, when the reception of the system real-time messages (F9)h  $\sim$  (FD)h is detected the detected message contents are set in the FIFO-IRx.

The FIFO-IRx is a 4-byte FIFO that processes the internal MIDI clock and keeps the process sequence of the system real-time data (messages) received by the receiver. When a selected MIDI clock timing signal (i.e., one of the MIDI clock timing signals of the MIDI

| ☐ MIDI clock interpolator     |                         | -MIDI message detector    |

|-------------------------------|-------------------------|---------------------------|

| Sequencer — Recording counter | MIDI clock controller – | FIFO-IRx                  |

| Playback counter              |                         | –MIDI message distributor |

message detector. SYNC detector and MIDI clock timer) is generated, the (F8)h is set in the FIFO-IRx. Also, the data (F9)h ~ (FD)h sent from the MIDI message detector are set in this FIFO buffer. If the (F8)h is present at the exit of the FIFO it is automatically brought out as the MIDI clock and sent to the MIDI message distributor, causing an interrupt signal to be issued. In case other system real-time message exists at the FIFO exit another interrupt signal is generated, and data is not brought out until directed by the host CPU.

The data at the exit of the FIFO-IRx can be arbitrarily read out from the host CPU, irrespective of the operation of the FIFO, eliminating the need to wait for the data processing by the FIFO-Rx. The MIDI message distributor controls the functional blocks whose operation depends upon the internal MIDI clock.

According to the (F8)h signal sent from the FIFO-IRx or to the host CPU direction, the distributor sends the MIDI clock signal simultaneously to each functional block. Also, by the direction of the host CPU, the system real-time messages (F9)h ~ (FD)h are sent to the functional blocks either independently or in unison, controlling their operation (start, stop and initialization).

The functional blocks controlled by this distributor are the CLICK counter, SYNC controller and sequencer. The loading of data into the FIFO-ITx is also controlled by the distributor.

### General-purpose timer

14-bit programmable interval timer (the same type as that for the MIDI clock timer)

This timer counts a fixed 8  $\mu$ sec clock. When the count of the values set in the register has been completed an interrupt signal is issued. The count restarts by the automatic load of the counter with the initial value.

# I/O controller

Functional block that provides the input/output control on the terminals P0 ~ P7.

Performs the setting of the I/O port input/output direction and of the output data. Both the input signal level at the input port terminal and the output signal level at the output port terminal can be read out.

IRQ controller

Controls the output level at the  $\overline{IRQ}$  terminal, status register and vector register, according to the 10 interrupt requests within the LSI and to the contents of the interrupt control register.

The status of interrupt requests is set by the bit map in the status register. The IRQ terminal output level goes low upon generation of an acknowledged interrupt request. From the interrupt requests acknowledged and being generated the vectors with high priority are set in the vector register. LSB of the vector is fixed at zero and the highest three bits are set by the host CPU.

### 2.3 Register layout

.

The register layout diagram is given in Fig. 2.3.

There are 38 registers built in to this LSI, as shown in this diagram. By way of example the register at the uppermost stage of the diagram is considered. R00 and IVR in this register are the register number and the register name, respectively. The register number's high-order digit and low-order digit are called the group number and the address number, respectively. A certain register can be accessed by first writing its group number into the R01 (RGR), then specifying its address number by the terminals A0  $\sim$  A2. Repeated group number entry into the R01 is not needed when the registers of the same group are to be accessed. The registers with the address numbers  $0 \sim 3$  (R00  $\sim$  R03) can always be accessed, irrespective of the group number.

Register functions are described in relevant chapters.

| register | R/¥        | content                         | 67           | b6           | 65           | 64        | 63         | b2         | 61             | 60          |

|----------|------------|---------------------------------|--------------|--------------|--------------|-----------|------------|------------|----------------|-------------|

| ROD IVR  | R          | IRO vector                      |              |              |              | IRO vecto | r          |            |                |             |

| RO1 RGR  | ¥          | system control                  | ю            | 1111         | 77777        | 1111      | re         | gister gro | no unu         | ल           |

| RO2 ISR  | 8          | IRO status                      |              |              |              | IRQ statu | 5          |            |                |             |

| RO3 ICR  | <b>Y</b>   | IRO clear request               |              |              |              | IRO clear | request    |            |                |             |

| RO4 IOR  |            | IRQ vector offset request       | 170          | vector of    | Tset         | (////     | /////      | [[]]]]     | [[[]]          | /////       |

| ROS IMR  | Y          | IRO mode control                | <u> </u>     | /////        | /////        | /////     | с/т        | 0/9        | VE             | VM          |

| ROG IER  | ¥          | IRD enable request              | L            |              |              | RO enab   | e          |            |                |             |

| R14 OMR  | Y          | MIDi realtime message control   | V////        | /////        | ASE          | MCE       | CDE        | MCDS       | M              | <b>៤</b> :ទ |

| R15 DCR  | ¥          | MIDI realtime message request   | Tx           | SYNC         | 22           | PC        | RC         | content    | of mes         | sade        |

| RIG DSR  | R          | FIFO-IRx data                   | 1            |              |              | FIFO-IRX  | data       |            |                |             |

| R17 ONR  | ¥          | FIFO-iRx control                | <u> </u>     | /////        | /////        | /////     | ////       |            | <u>////</u>    | CLK         |

| R24 RRR  |            | Rx communication rate           | V////        | /////        | Rx0/F        |           | Rx comn    | nunication | n <i>ra</i> te |             |

| R25 RMR  |            | Rx communication mode           | <u>V////</u> | <u>/////</u> | RXCL         | RXPE      | RXPL       | RxE/O      | R×SL           | RxST        |

| RIG AMR  | ¥          | Address-hunter control          | IDCL         |              |              | maker ID  | cade       |            |                |             |

| R27 ADR  | 4          |                                 | BRDE         |              |              | device ID | code       |            |                |             |

| R34 RSR  | R          | FIFO-Rx status                  | RXRDY        | RXOV         | R×F          | RxP       | BRK        | RXUL       | AHBSY          | RxBSY       |

| R35 RCR  | Y          | FIFO-Rx control                 | RxC          | RXOVC        | <u> ////</u> | FLTE      | SRKC       | RXULC      | AHE            | RxE         |

| R36 RDR  | R          | FIFO-Rx data                    | 1            |              |              | FIFO-Rx   | data       |            |                |             |

| R44 TRR  | $  \vee  $ | Tx communication rate           | V////        | TxRx         | Tx0/F        |           | Tx comn    | nunication | nrate          |             |

| R45 TMR  | ¥          | Tx communication mode           | <u> </u>     | ////         | TxCL         | TXPE      | TXPL       | TxE/O      | TxSL           | TxST        |

| R54 TSR  | R          | FIFO-Tx status                  | TXEMP        | TXBSY        | V////        | /////     | /////      | TxiDL      | []]]           | Tx8SY       |

| RES TCR  | ¥          | FIFO-Tx control                 | TxC          | <u> </u>     |              | ////      | BLXE       | TXIDLC     | <u> []]]</u>   | TxE         |

| R56 TDR  | ¥          | FIFO-Tx data                    |              |              |              | FIFO-TX   | data       |            |                |             |

| R64 FSR  | R          | FSK status                      | RXFS         | SS           | CSF          | CFF       | (///       | ]]]]]      | PS             | PDF         |

| R65 FCR  | Y          | FSK control                     | ME           | <i>[]]]</i>  | ////         | CFC       | DE         | APD        | P/N            | PDFC        |

| R66 CCR  | ¥          | Click counter control           | <u> </u>     | /////        | /////        |           |            |            | CLKM           | OUTE        |

| R67 CDR  | ¥          | Click counter load value        | LD           |              |              | 7 bit dat | a to load  |            |                |             |

| R74 SRR  | R          | Recording counter current value |              |              |              | 8 bit dat | a of curr  | ent value  |                |             |

| R75 SCR  | ¥          | Sequencer control               | VIII         | [[[[         | ADO          | CLR       | 4 b        | it interpo | lation r       | ite         |

| R76 SPRL | ¥          | Blass basis annat a sa lua      |              |              |              | lower 8   | bit data t | o add      |                |             |

| R77 SPRH | ¥          | Play-back counter vakie         |              | 1            |              | higher 7  | bit data   | to add     |                |             |

| R84 GTRL | ¥          | 6                               |              |              |              | lower 8   | bit data t | o load     |                |             |

| R85 GTRH | ¥          | General timer value             | LD           | <u> </u>     | 1            | higher 6  | bit data   | to load    |                |             |

| R86 MTRL | Y          |                                 |              |              |              | lower 9   | bit data t | o load     |                |             |

| 887 MTRH | 4          | MIDi-clock timer value          | LD           | <u>V////</u> | 1            | higher 6  | bit data   | to load    |                |             |

| R94 EDR  | W          | External I/O direction          |              |              |              | direction | of earch   | 1/O port   |                |             |

| R95 EOR  | 1¥         | External I/O output data        |              |              |              | output re | quest fa   | r 1/0 port | ł              |             |

| R96 EIR  | R          | External I/O input data         |              |              |              | pin level | of earch   | 1/0 port   |                |             |

| A2, A1, A0 = 000 | 001     | 010     | 011     | 100      | 101      | 110      | 111      |

|------------------|---------|---------|---------|----------|----------|----------|----------|

| group-0          |         | T       | [       | RO4 IOR  | ROS IMR  | RO6 IER  |          |

| 1                |         |         |         | R14 DMR  | R15 DCR  | R16 DSR  | R17 DNR  |

| 2                |         |         |         | R24 RRR  | R25 RMR  | R26 AMR  | R27 ADR  |

| 3                |         |         |         | R34 RSR  | R35 RCR  | R36 RDR  | V/////// |

| 4                |         |         |         | R44 TRR  | R45 TMR  | VIIIII   | <u> </u> |

| 5 RCC IVR        | RO1 RGR | RO2 ISR | ROJ ICR | RS4 TSR  | R55 TCR  | R56 TDR  | <u> </u> |

| 6                |         |         |         | R64 FSR  | R65 FCR  | R66 CCR  | R67 CDR  |

| 7                |         |         |         | R74 SRR  | R75 SCR  | R76 SPRL | R77 SPRH |

| 8                |         |         |         | RS4 GTRL | R85 GTRH | R86 MTRL | R87 MTRH |

| 9                |         |         |         | R94 EDR  | R95 EOR  | R96 EIR  | V//////  |

Figure 2.3 Register map

### 3. COMMUNICATION FUNCTIONS

### 3.1 Serial communication

#### 3.1.1. Communication method

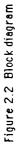

Fig. 3.1 illustrates the message format of the asynchronous serial communication employed in the YM3523. There are several modes of message format, depending upon the data bit length, the existence of parity bit, the parity bit length, the stop bit length and the type of stop bit.

The data bit length of seven or eight bits is treated as one character.

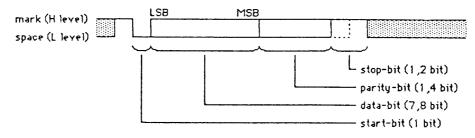

The parity bit modes are one-bit, four-bit and no parity, and odd or even parity can be used. In the four-bit parity mode, a pair of data bits correspond to one parity bit, as shown in Fig. 3.2.

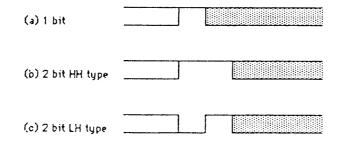

The stop bit length are one or two bits, and two modes exist for the two bits length, i.e., one mode with two consecutive marks (H level) and the other mode with one mark and one space (L level). Fig. 3.3 indicates the stop bit modes.

The communication rates available are 1/16 or 1/32 of the input clock rate supplied to the CLKM terminal, or 1/32nd, 1/64th, ...., 1/8192nd of the input clock rate to the CLKF terminal. By inputting a clock of 1MHz or 0.5MHz to the CLKM terminal and MIDI communication rate of 31.25K bps can be obtained. And, if 614.4KHz is input to the CLKF terminal communication rates of from 75 bps to 19200 bps (75 x  $2^{n}$  series) are available.

If the signal for the magnetic tape is handled by the internal FSK modulator and demodulator, the use of several CLKM communication rates (i.e., 1/16th and 1/32nd of the input) is inhibited.

### 3.1.2. Transmission procedure

When the transmit operation is acknowledged by the host CPU and data is set in the FIFO-Tx or FIFO-ITx, the transmitter adds the start bit, parity bit and stop bits to the data according to the transmit mode and transmits the data at the selected communication rate. When the data bit length is seven bits the MSB of the data set in the FIFO is ignored.

The transmitter output is sent direct to the TxD terminal or sent to the FSK modulator where the output is FSK-modulated per bit which is then routed to the TxF terminal.

### 3.1.3. Reception procedure

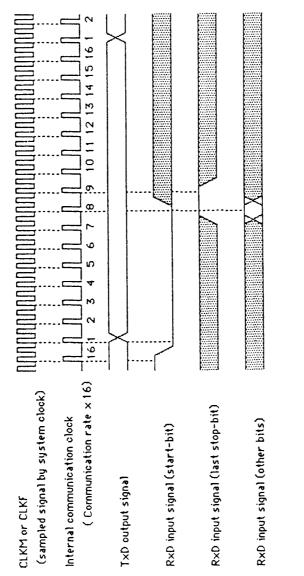

How the input signal to the RxF terminal is received is explained using Fig. 3.4. The receiver samples the input signal with the internal communication clock that is 16 times the communication rate (obtained by dividing the input clock at CLKM or CLKF terminal). If, under "waiting for a new message" condition, the receiver samples a space (L level) eight times after at least one mark (H level), it is recognized as a start bit. The eighth timing of the internal communication clock in this space condition is used as a midpoint of the start bit. Then the input sampling is performed by using every 16th clock of the internal communication clock as a midpoint for each bit, i.e., data bit, parity bit and stop bit. At the time when the last stop bit is sampled the receiver will go into the wait state for a next message.

Figure 3.1 Communication signal format

Figure 3.2 Data-bit, parity-bit relation in 4 bit parity mode

Figure 3.3 Stop-bit length and type

In the case of the reception of the FSK-modulated signal that is input to the RxF terminal, since the FSK demodulator generates a clock signal every time each bit is demodulated the per-bit sampling is performed based upon this clock. The start bit detection is made by the continuous reception of marks and spaces.

In either case, upon completion of the reception of one message 0 is added to the MSB in the case of the seven-bit length mode to form an eight-bit data signal. And, if any abnormal condition exists with the parity and stop bits the Parity Error and Framing Error signals are made active. These signals are loaded into the FIFO-Rx via the MIDI clock filter and address hunter and are accessible from the host CPU.

### 3.1.4. Operation of transmitter and receiver

The communication rate, communication mode (communication format) and wiring of the transmitter and receiver are set by means of registers R24, R25, R44 and R45. Register operations are prohibited when the transmitter and/or receiver are in operation. Fig. 3.5 shows the function of each register.

• TxRx (R44 - b6) - WRITE -

If 1 is set to the TxRx, the input to the RxD terminal is unconditionally sent to the TxD terminal.

• TxD/F (R44 - b5), RxD/F (R24 - b5) - WRITE -

If 0 is already set to the TxD/F, the transmitter serial output signal is sent to the TxD terminal as long as 1 is not set to the TxRx. At this time the serial input signal to the FSK modulator is the CLICK counter output signal to the CLICK terminal, and modulation is conducted at a rate of 1200bps (CLKF/512). If 1 is set to the TxD/F, then the transmitter serial output signal becomes the serial input signal to the FSK modulator, and modulation is performed at the transmitter's communication rate. As long as 1 is not set to the TxRx the output at the TxD terminal has the H level. If 0 is already set to the RxD/F, the input signal to the RxD terminal is used as the receiver input signal. At this time the FSK demodulator performs demodulation at a modulation rate of 1200 bps (CLKF/512), and its serial output signal is sent to the SYNC detector. If 1 is sent to the RxD/F, the FSK demodulator serial output signal becomes the receiver input, and the FSK demodulator conducts its operation at the communication rate of the receiver.

•  $R44 - b4 \sim b0, R24 - b4 \sim b0$  - WRITE -

According to the values set to these bits the communication rate of the transmitter and receiver is determined. By changing the input frequency to the CLKM and CLKF terminals the communication rate of the  $110 \times 2^n$  series, etc., can be realized. However, this alternation has an effect on the internal timers, SYNC and CLICK output pulse width and the active sense function.

| R24 RRR | W Rx communication rate              |                     |                                                                   |

|---------|--------------------------------------|---------------------|-------------------------------------------------------------------|

|         |                                      |                     |                                                                   |

| R×D/F   | select Receiver input connection     | 0 : R×D             | 1 : FSK demodulator                                               |

|         | communication rate                   | 00xxx : CLKM/16     | $(31250 \text{ bps}) = \text{ inhibited while } R \times D/F = 1$ |

|         |                                      | 01××× : CLKM/32     | (15625 bps) inhibited while R×D/F = 1                             |

|         |                                      | 10××× : CLKF /32    |                                                                   |

|         | CLKF = 614.4 KHz )                   | 11000 : CLKF /64    | ( 9600 bps)                                                       |

|         |                                      | 11001 : CLKF/128    | (4800 bps)                                                        |

|         |                                      | 11010 : CLKF /256   | ( 2400 bps)                                                       |

|         |                                      | 11011 : CLKF /512   | ( 1200 bps)                                                       |

|         |                                      | 11100 : CLKF /1024  | ( 600 bps)                                                        |

|         |                                      | 11101 : CLKF / 2048 | ( 300 bps)                                                        |

|         |                                      | 11110 : CLKF /4096  | ( 150 bps)                                                        |

|         |                                      | 11111 : CLKF /8192  | ( 75 bps)                                                         |

| R25 RMR | ¥ Rx communication mode              | <b></b>             |                                                                   |

|         |                                      |                     |                                                                   |

|         |                                      |                     |                                                                   |

| R×CL    | select data bit length               | 0 : 8 bit           | 1 : 7 bit                                                         |

| RxPE    | enable parity-bit check              | 0 : disable         | 1 : enable                                                        |

| R×PL    | select parity-bit length             | 0 : 1 bit           | 1 : 4 bit                                                         |

| R×E/0   | select parity-bit polarity           | 0 : even            | bbo: 1                                                            |

| RxSL    | select stop-bit length               | 0 : 1 bit           | 1 : 2 bit                                                         |

| R×ST    | select stoo-bit tupe in 2 bit length | HH O                | H                                                                 |

| $\sim$    |

|-----------|

|           |

| ~ ~       |

| -         |

| <b>C</b>  |

| 0         |

|           |

| ~         |

| చ         |

|           |

|           |

|           |

| 7         |

|           |

| Ē         |

| 5         |

| - 2       |

| 0         |

| is) comm  |

| 8         |

| Ē         |

|           |

| ్ల        |

| ၈         |

| 5         |

| 9         |

| -         |

| ons f     |

| č         |

| 2         |

|           |

| -         |

| ്         |

| <b>C</b>  |

| 3         |

| ~         |

| -         |

|           |

| ÷         |

| ົ         |

| - جمع     |

| - Ö       |

| မ         |

| $\propto$ |

|           |

| S         |

| •         |

| N)        |

|           |

| دە        |

| 5         |

| -         |

| Ū,        |

| 1         |

|           |

|           |

| R44 TRR   | ZR     | W Tx communication rate              |                                                                               |

|-----------|--------|--------------------------------------|-------------------------------------------------------------------------------|

| b7        |        |                                      |                                                                               |

| b6 Tx     | TxRx   | select TxD connection                | 0 : transmitter 1 : R×D                                                       |

| b5 Tx     | T× n/F | select transmitter output connection | 0 : TxD 1 : FSK modulator                                                     |

| <b>b4</b> |        | cornrnunication rate                 | 00xxx : CLKM/16 (31250 bps) inhibited while TxD/F = 1                         |

| ∽Qq       |        | ( in Ct KM = 0.5 MHz                 | $01 \times x \times : CLKM/32$ (15625 bps) inhibited while $T \times D/F = 1$ |

| 2         | -      |                                      | Ŭ                                                                             |

|           |        | ULKF = 614.4 KHz                     | $\sim$                                                                        |

|           |        |                                      | 11001 : CLKF / 128 ( 4800 bps)                                                |

|           |        |                                      | CLKF / 256 (                                                                  |

|           |        |                                      | : CLKF /512 (                                                                 |

|           |        |                                      | CLKF/1024 (                                                                   |

|           |        |                                      | 11101 : CLKF /2048 ( 300 bps)                                                 |

|           |        |                                      | $\sim$                                                                        |

|           |        |                                      | 11111 : CLKF / 8192 ( 75 bps)                                                 |

|           |        |                                      |                                                                               |

| R45 TMR   | ٦R     | W Tx communication mode              |                                                                               |

| b7        |        |                                      |                                                                               |

| b6        |        |                                      |                                                                               |

| b5 T×     | T×CL   | select data-bit length               | 0 : 8 bit 1 : 7 bit                                                           |

| b4 T×     | T×PE   | enable parity-bit generation         | 0 : disable 1 : enable                                                        |

| b3 T×     | T×PL   | select parity-bit length             | 0 : 1 bit 1 : 4 bit                                                           |

| b2 Tx     | T×E/0  | select parity-bit polarity           | 0 : even 1 : odd                                                              |

| b1 Tx     | T×SL   | select stop-bit length               | 0:1 bit 1:2 bit                                                               |

| b0 T×ST   | (ST    | select stop-bit type in 2 bit length | 0 : HH 1 : LH                                                                 |

| 'unctions for serial communication (2) |

|----------------------------------------|

| s for serial                           |

| r functions                            |

| 5 Register                             |

| Figure 3.5                             |

- TxCL (R25 b5), RxCL (R25 b5) WRITE -Determines the data bit length of the communication message.

- TxPE (R45 b4), RxPE (R25 b4) WRITE Determines whether parity is used or not.

- TxPL (R45 b3), RxPL (R25 b3) WRITE Determines the parity bit length.

For the seven-bit data length one-bit parity is used, irrespective of the setting of this bit.

- TxE/O (R45 b2), RxE/O (R25 b2) WRITE Determines the parity bit polarity.

- TxSL (R45 b1), RxSL (R25 b1) WRITE Determines the stop bit length.

- TxST (R45 b1), RxST (R25 b1) WRITE Determines the type of stop bit. If, for a stop bit length of 2, 0 is set to this bit, 2 bits of mark (H level) is treated as stop bits; if 1 is set instead stop bits consists of one bit of space (L level) and one bit of mark. When a stop bit length is 1 setting of this bit is invalid.

- 3.1.5. Effects of the initial clear Refer to sections 3.3 & 3.4.

### 3.2 Magnetic tape interface (FSK modulation)

# 3.2.1. Modulation method

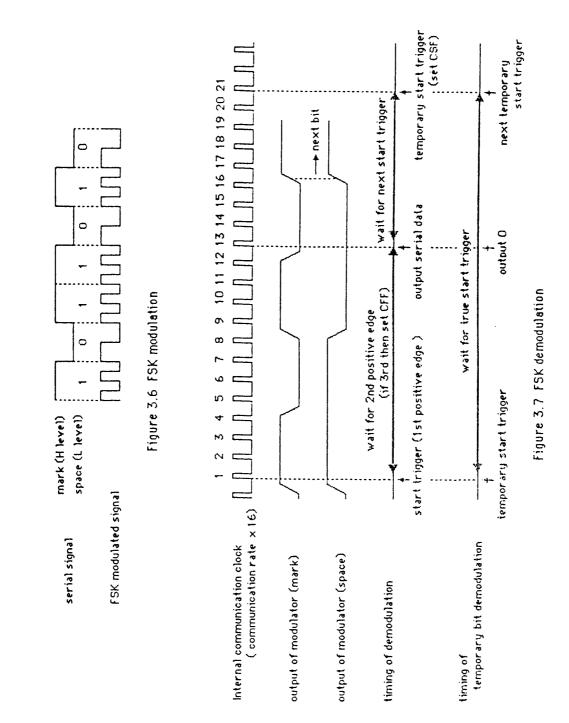

Fig. 3.6 shows the serial data and the FSK-modulated signal used in the YM3523.

As can be seen from this figure, the FSK-modulated signal is produced by replacing marks (1s) and spaces (0s) in the serial data with two square waves and one square wave, respectively. When this signal is recorded and then reproduced by an audio cassette tape recorder, etc., distortions arise locally or wholly in the duty ratio and the communication rate; however, performing demodulation in synchronization with one- or two-wave signal can cope with these distortions.

### 3.2.2. Modulation procedure

When the modulation operation is acknowledged by the host CPU, the FSK modulator receives at the prescribed transfer rate the transmitter serial output signal or the SYNC output signal of the SYNC controller, modulates this signal and sends the modulated signal to the TxF terminal. In this case, the modulation rate for the transmitter serial output equals to the transmitter communication rate, while a modulation rate of 1200 bps is employed for the SYNC output signal. The CLKM communication rates of 1/16th and 1/32nd of the input frequency cannot be used.

### 3.2.3. Demodulation procedure

When the demodulation operation is acknowledged by the host CPU, the FSK demodulator demodulates the FSK-modulated signal which is input to the RxF terminal, and sends the serial signal to the receiver or the SYNC detector. If the serial data is to be sent to the receiver, the demodulation rate is determined by the communication rate set by the receiver. In this case, as described later, a clock signal is sent from the demodulator to the receiver each time one bit is demodulated, and the receiver samples the actual serial data using this clock. The CLKM communication rates (1/16th and 1/32nd of the input frequency) cannot be employed.

A demodulation rate of 1200 bps is used in the case of sending the serial data to the SYNC detector.

The operation of the FSK demodulator is described using Fig. 3.7. The internal communication clock – either 16 times the receiver communication rate or 16 times 1200 bps – is first produced. The input signal to the RxF terminal is read in synchronization with this clock, and its rising edge is detected. The first rising edge detected is regarded as the start timing for one bit, and the internal communication clock counter is set to 1. If the next rising edge is detected before the count of 13th clock, the serial output is set to the H level in synchronization with the 13th clock; if not detected it is set to the L level. The DSF (demodulated status flag) in the R64 (FSK status register) is set accordingly. At the same time, a clock signal is sent to the receiver to indicate the completion of one bit demodulation.

If more than one input signal rising edge is detected before the 13th clock, the CFF (carry first flag) in the R64 is set. Also, when the next input signal positive edge cannot be detected before the 21st clock, the CSF (carry slow flag) of the R64 is set. The 21st clock is regarded as the start timing for a temporary bit and the internal communication clock counter is set to 1. Then the serial output is set to the L level in synchronization with the 13th clock, and at the same time a clock is sent to the receiver. At the 21st clock the counter is again set to 1. This cycle is repeated

until the input signal positive edge is detected. When the positive edge is finally detected usual one bit process described above restarts. Although the serial output in the case of a temporary bit is treated as the L level within the demodulator, and the DSF of the R26 has the L level, the serial signal being sent to the receiver and the SYNC detector has the H level.

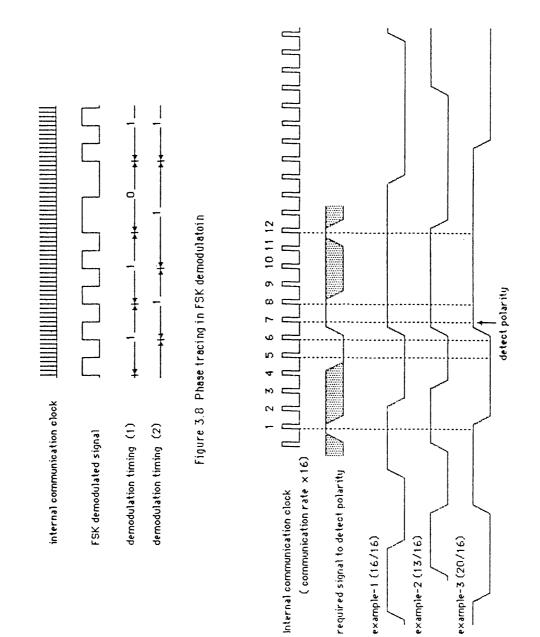

Fig. 3.8 illustrates the manner in which the phase alignment of the FSK-modulated signal is accomplished by the FSK demodulator. When demodulation starts from the serial signal mark (two wave-modulated signal = H level), it tends to be  $180^{\circ}$  out-of-phase, as shown in Fig. 3.8 (1) & (2). As is apparent from the figure, there is a possibility for one bit of space (one wave-modulated signal = L level) to be overlooked.

The polarity (H and L levels) inversion can be applied to the input signal from the RxF terminal to the demodulator. The positive or negative polarity can be specified from the host CPU, or according to the result from the internal polarity detection circuit the automatic polarity follow-up system functions.

The operation of this polarity detection circuit is described using Fig. 3.9. The input signal at the RxF terminal is loaded into the 12-bit shift register according to the internal communication clock. Then the data are extracted from the register in synchronization with the 1st, 5th, 6th, 7th, 8th and 12th clocks (counting from the oldest data stage of the register). If the data synchronized with the 5th and 6th clocks only have different values from other data, the data before the 6th clock are considered mark (two wave modulation), while the data after the 7th clock are regarded as space (one wave modulation). If the space start position is known the direction of the input signal change at the start corresponds to the positive direction.

In Fig. 3.9 three types of input signals, each with a slightly different communication rate from the others, are given as an example. Polarity decision will be made for the input signal whose phase is opposite to that of the three input signals shown.

In the automatic polarity follow-up conducted according to the detected polarity the phase alignment is made in accordance with the timing of the mark-to-space transition detected during the polarity detection, and the internal communication clock counter is set to 1.

In the case of the automatic polarity decision the requirements for the input signal duty ratio are considerably strict. To prevent the dropout of bits in phase alignment it is desirable that the recorded data header portion have a mixture of marks and spaces and that use be made of the algorithm that the polarity is fixed after repeated decisions.

3.2.4. Operation of the FSK modulator and demodulator

The operation of the FSK modulator and demodulator is controlled by the register R65. The status of the FSK demodulator is set in the register R64, and can be read out at any time. Fig. 3.10 shows the function of each register.

• RxFS(R64 - b7) - READ -

Status flag that indicates the input level at the RxF terminal.

- SS (R64 b6) READ Status flag that indicates the result of demodulation.

A temporary bit (see section 3.2.3.), when demodulated, is treated as space (L level).

- CSF (R64 b5) READ -

If the RxF input signal positive edge cannot be detected for a period equal to 21 clocks by the internal communication clock or 21/16th of a bit counting from the start of any one bit, 1 is set. This flag denotes that a signal with the communication rate slower than the prescribed demodulation rate may be input.

• CFF (R64 - b4) - READ -

If more than one positive edge from the RxF input signal is detected during the period equal to 12 clocks by the internal communication clock or 12/16th of a bit counting from the start of any one bit, 1 is set. This flag indicates that a signal with the communication rate faster than the prescribed demodulation rate may be input.

- PS (R64 b1) READ -The detection result of the R x F input signal polarity is set in this status flag.

- PDF (R65 b0) READ -This flag is set when the polarity detection is made.

- ME (R65 b7) WRITE -If 1 is already written the FSK modulator operates; if 0 is written its operation stops.

- CFC (R65 b4) WRITE -If 1 is written 0 is set in the CSF and CFF.

- DE (R65 b3) WRITE -If 1 is already written the FSK demodulator operates; if 0 is written its operation stops.

| 0,10    | R F5K Status                     |                       |                           |

|---------|----------------------------------|-----------------------|---------------------------|

| XXIO    | KXP pin status                   | 0 :L level            | 1 : H level               |

| SS      | demodulated serial signal status | 0 : space ( L )       | 1 : mark ( H )            |

| CSF     | carrier slow detected flag       | + .<br>G              | 1 : carrier slow detected |

| CFF     | carrier fast detected flag       | -: 0                  | 1 : carrier fast detected |

|         |                                  |                       |                           |

| PS      | polarity status                  | G : positive          | i : negative              |

| PDF     | polarity detected flag           | - : 0                 | 1 : polarity detected     |

| R65 FCR | ₩   FSK control                  |                       |                           |

| ME      | enable Modulator                 | 0 : disable           | 1 : enable                |

|         |                                  |                       |                           |

| CFC     | clear carrier S/F detected flag  | write 1 to clear flag |                           |

| DE      | enable Demodulator               | 0 : disable           | i : enable                |

| APD     | disable auto polarity detector   | 0 : enable            | 1 : disable               |

| P/N     | set polarity by manual           | 0 : positive          | 1 : negative              |

| PDFC    | clear polarity detected flag     | write 1 to clear flag |                           |

| Figure 3.10 Register functions for FSK Modulator/Demodulator |  |

|--------------------------------------------------------------|--|

| Re                                                           |  |

| Figure 3.10                                                  |  |

• APD (R65 – b2) – WRITE –

If 0 is already written the automatic polarity follow-up function operates. If 1 is written, the input polarity is determined according to the subsequent P/N bit (see below) and demodulation is performed.

- P/N (R65 b1) WRITE Sets the input polarity when the automatic polarity follow-up function is not used.

- PDFC (R65 b0) WRITE -If 1 is written 0 is set in the PDF.

- 3.2.5. Effects of the initial clear Refer to section 3.3 & 3.4.

# 3.3 Functions related to transmitting

### 3.3.1 FIFO-ITx and FIFO-Tx

The FIFO-ITx is a 4-byte transmitting buffer intended exclusively for the MIDI system realtime messages (F8)h ~ (FE)h. For details, refer to section 4.1: "MIDI clock controller and related functions".

The FIFO-Tx is a general-purpose 16-byte transmitting buffer. If data is set in this buffer from the host CPU, the data will be sent to the transmitter in the set order. The flag showing the FIFO is not full and the flag showing the empty FIFO condition can be read out from the host CPU. If the FIFO-Tx becomes empty because of the read-out by the transmitter an interrupt signal will be sent to the IRQ controller.

The transmitter gives priority to the data (if present) of the FIFO-ITx; therefore, the data in this buffer will first be read out and transmitted.

#### 3.3.2. Idle detector

Detects the long absence of transmit operation.

If there is no transmission for approximately 80msec (equal to the time of six counts of the signal obtained by dividing the input clock at the CLKF terminal by  $2^{13}$ : if CLKF = 614.4KHz, then clock interval = 13.4msec, time = 66.7 - 80.1msec), the flag is set, and the active sense message (FE)h is set in the FIFO-ITx if already acknowledged by the host CPU. The same operation will be repeated every sixth counts. For the acknowledgment of the setting of the (FE)h in the FIFO-ITx, see section 4.1: "MIDI clock controller and related functions".

# 3.3.3. Transmitter and FSK modulator

Refer to section 3.1 for the transmitter, and section 3.2 for the FSK modulator.

An auxiliary function of the transmitter is the BREAK character transmit function. If instructed by the host CPU the transmitter goes to the L level and will maintain that level until released. In this case the internal transmit operation of the transmitter continues without interruption.

#### 3.3.4. Register operation

The transmission-related functions are controlled by the registers R54, R55 and R56. Fig. 3.11 shows the function of each register.

- TxEMP (R54 b7) READ -Status flag that indicates the FIFO-Tx is empty.

- TxRDY(R54 b6) READ -

Status flag that indicates the FIFO-Tx is not full and hence data can be set. If this flag is 0, additional data, if sent to FIFO-Tx, will be lost.

|                  | 0 : data exist 1 : empty    | 0 :FIFO-Tx full 1 : ready   |          | 0 : 1 : Tx idle detected |    | 0 : idle 1 : busy     |                   | write 1 to clear FIFO-Tx & FIFO-ITx |          | 0 :- 1 : set Tx output signal as L level | write 1 to clear flag     |    | 0 : disable 1 : enable |                | 8 bit data          |  |

|------------------|-----------------------------|-----------------------------|----------|--------------------------|----|-----------------------|-------------------|-------------------------------------|----------|------------------------------------------|---------------------------|----|------------------------|----------------|---------------------|--|

| R FIFO-T× status | b7 TxEMP FIFO-Tx empty flag | b6 TxRDY FIFO-Tx ready flag |          | Tx idle detected flag    |    | Transmitter busy flag | W FIFO-Tx control | clear FIFO-Tx & FIFO-IT×            |          | enable send break                        | TxIDLC clear Tx idle flag |    | enable Transmitter     | ₩ Fif0-T× data | set data to FIFO-T× |  |

| R54 TSR          | b7 TxEMP                    | bE T×RDY                    | b5<br>b3 | b2 T×IDL                 | P1 | b0 T×BSY              | R55 TCR           | b7 TxC                              | b6<br>54 | b3 BRKE                                  | b2 TxIDLC                 | b1 | b0 T×E                 | R56 TDR        | 67<br>∳0            |  |

Figure 3.11 Register functions for Transmitter

• TxIDL (R54 - b2) - READ -

This flag is set each time non-transmit condition of approximately 80 msec (when CLKF = 614.4KHz) is detected by the idle detector.

- TxBSY (R54 b0) READ -Status flag that indicates the transmitter is in transmit operation.

- TxC (R55 b7) WRITE -Clears the contents of the FIFO-ITx and FIFO-Tx. The IRQ is not generated.

- BRKE (R55 b3) WRITE If 1 is written the transmitter serial output goes to the L level and stays there until 0 has been written. The transmitter internal operation continues during the L level period.

- TxLDLC (R55 b2) WRITE -Clears the TxIDL flag.

- TxE (R55 b0) WRITE -Enables the transmitter operation. When its operation is inhibited by writing 0 a character now under transmission will be transmitted completely. Read-out of a new character from the FIFO-Tx and FIFO-ITx is inhibited.

- R56 b7 ~ b0 WRITE -Data written into this register is set in the FIFO-Tx.

- 3.3.5. Note on IRQ

If the FIFO-Tx becomes empty because of the read-out by the transmitter an interrupt signal is sent to the IRQ controller. This signal is cleared by the operation on the IRQ controller or if the TxEMP flag becomes zero.

# 3.3.6. Effects of initial clear

The initial clear of the hardware and software will cause the following operations to be made:

- The TxD and TxF terminal outputs go to the H level and the L level, respectively.

- The operation of the transmitter and FSK modulator is stopped and initialized.

- Idle counter starts its count from zero.

- Zeros are written into the registers.

- All flags other than the status flags are cleared.

### 3.4 Functions related to receiving

## 3.4.1. FIFO-Rx

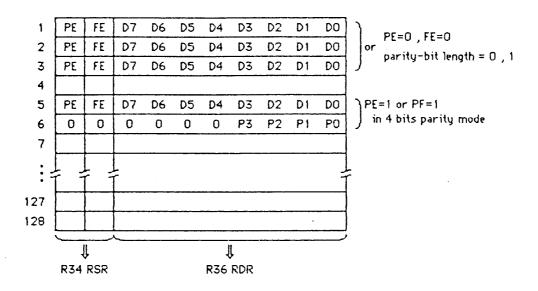

The FIFO-Rx is a receiving buffer of 10 bits x 128 words. Fig. 3.12 illustrates its configuration.

When the receiver receives one character of message the 8-bit data and the 2-bit error flag are set in the FIFO-Rx. If the data is read out by the host CPU the data in the FIFO-Rx is automatically forwarded. The error flag associated with the data to be read next can be read out by the status register RST (R34).

In the 4-bit length parity mode if any error is detected one word consisting of the 4-bit parity error flag 6 zeros is set in the FIFO-Rx following the 8-bit data plus 2-bit error flag.

The flag indicating that the FIFO has the data to be read out and the flag indicating that the FIFO under the full condition is provided with new data (i.e., overflow condition) can be read out by the host CPU. If the FIFO goes into the overflow state, the flag is set and at the same time the second oldest data (one word) is lost, the data that follows is forwarded and the latest data is set. Because of this, when the host CPU detects the framing error, parity error and overrun error, one word of data is abandoned, thereby guaranteeing the data thereafter.

If new data is set in the empty FIFO an interrupt signal is sent to the IRQ controller.

### 3.4.2. Break detector

Detector circuit for the BREAK condition.

When the receiver input signal has the L level for the period of two characters according to the reception mode and rate currently set, the flat is set and an interrupt signal is sent to the IRQ controller. The interrupt cannot be used at the same time with that from the off-line detector (see below).

### 3.4.3. Off-line detector

Detects the long absence of receive operation. If there is no parallel data output from the receiver for approximately 300msec (equal to the time of 24 counts of the signal obtained by dividing the input clock at the CLKF terminal by  $2^{13}$  : if CLKF = 614.4KHz, then clock interval = 13.4msec, time = 308.2 - 321.6msec), the flag is set and an interrupt signal is sent to the IRQ controller. The interrupt cannot be used at the same time with that from the break detector (see above).

# 3.4.4. MIDI clock filter

Circuit to eliminate the MIDI clock message (F8)h from the received data. If this flag is enabled by the host CPU, the setting of data in the FIFO-Rx is inhibited only when the (F8)h is received without error.

Figure 3.12 FIFO-Rx structure

# 3.4.5. Address hunter

Circuit to eliminate the special format data train referred to as the MIDI system exclusive message. If enabled, by the host CPU, the setting of the unnecessary system exclusive message data received without error into the FIFO-Rx is inhibited.

For details, see section 4.4 "Address hunter".

# 3.4.6. Receiver and FSK demodulator

See section 3.1 for the receiver, and section 3.2 for the FSK demodulator.

3.4.7. Register operations

Transmission-related functions are controlled by the registers R34 and R35. Refer to section 4.4 for address hunter controls.

- RxRDY (R34 b7) READ -Status flag that shows the FIFO-Rx has the data to be read out.

- RxOV (R34 b6) READ -Flag that shows the overflow has occurred in the FIFO-Rx.

- RxF (R34 b5) READ -Framing error flag for the next data to be read out.

- BRK (R34 b3) READ -Flag that indicates the BREAK condition has been detected.

|                  | 1 : data ready     | 1 : overflow detected          | 1 : framing error detected | 1 : parity error detected | 1 : break detected  | 1 : off-line detected  | 1 : Address-hunter busy  | 1 : Receiver busy  |                   |                          |                              |    | 1 : enable               |                           |                              | 1 : enable            | 1 : enable      |                |                       |                     |

|------------------|--------------------|--------------------------------|----------------------------|---------------------------|---------------------|------------------------|--------------------------|--------------------|-------------------|--------------------------|------------------------------|----|--------------------------|---------------------------|------------------------------|-----------------------|-----------------|----------------|-----------------------|---------------------|

|                  | 0 : empty          | -: 0                           | -: 0                       | -: 0                      | -: 0                | -: 0                   | 0 : Address-hunter idle  | 0 : Receiver Idle  |                   | write 1 to clear FIFO-Rx | write 1 to clear flag        |    | 0 : disable              | write I ti clear fiag     | write 1 to clear flag.       | 0 : disable           | 0 : disable     |                | 8 bit data            |                     |

| R FIFO-R× status | FIFO-Rx ready flag | FIFD-Rx overflow detected flag | framing error flag         | parity error flag         | break detected flag | off-line detected flag | Address-hunter busy flag | Receiver busy flag | ₩ FIFO-R× control | clear FIFO-Rx            | clear overflow detected flag |    | enable MIDI-clock Filter | clear break detected flag | clear off-line detected flag | enable Address-hunter | enable Receiver | R FIFO-RX data | get data from FIFO-R× | & increment FIFO-Rx |

| R34 RSR          | b7 R×RDY           | b6 R×0V                        | b5 RxF                     | b4 RxP                    | b3 BRK              | b2 R×OL                | b1 AHBSY                 | b0 R×BSY           | R35 RCR           | b7 RxC                   | b6 Rx0VC                     | b5 | b4 FLTE                  | b3 BLKC                   | b2 R×OLC                     | b1 AHE                | b0 R×E          | R36 RDR        | þ7                    | bÔ                  |

| Figure 3.13 Register functions for Receiver |

|---------------------------------------------|

| Figure 3.13                                 |

- RxOL (R34 b2) READ -Flag that indicates the off-line condition has been detected.

- AHBSY (R34 b1) READ -Status flag that shows the operating address hunter detects the MIDI system exclusive message and is processing it.

- RxBSY (R34 b0) READ -Status flag that shows the receiver receives the serial data and is converting this data to the parallel equivalent.

- RxC (R35 b7) WRITE -Clears the contents of the FIFO-Rx.

- RxOVC (R35 b6) WRITE Clears the RxOL flag.

- FLTE (R35 b4) WRITE -Enables the operation of the MIDI clock filter.

- BLKC (R35 b3) WRITE Clears the BLK flag.

- RxOLC (R35 b2) WRITE -Clears the RxOL flag.

- AHE (R35 b1) Enables the operation of the address hunter.

- RxE (R35 b0) Enables the operation of the receiver.

- R36 b7 ~ b0 Reads the first (oldest) data of the FIFO-Rx. The data in the FIFO is automatically forwarded when the read-out is performed.

# 3.4.8. Note on IRQ

If the empty FIFO-Rx receives the parallel data from the receiver, an interrupt signal is sent to the IRQ controller. This interrupt is cleared by operating upon the IRQ controller, or when the FIFO-Rx becomes empty by the read-out of data.

The interrupt signal from the break detector and the off-line detector to the IRQ controller reflects the contents of the BRK and RxOL flags. This signal is cleared by operating upon the IRQ controller, or cleared simultaneously if the BRK and RxOL flags are cleared. Conversely, the operation of the IRQ controller causes the BRK and RxOL flags to be cleared.

The simultaneous use of both IRQs from the host CPU is impossible.

# 3.4.9. Effects of the initial clear

The initial clear of the hardware and software will cause the following operations to be made:

- The operation of the receiver and FSK demodulator is stopped and both are initialized.

- The count of the break detector and off-line detector starts at zero.

- Registers are written with zeros.

- Flags other than status flags are cleared.

# 4. MIDI SERVICE FUNCTIONS

### 4.1 MIDI clock controller and related functions

#### 4.1.1. Purpose of the MIDI clock controller

The MIDI system real-time message includes the clock message (MIDI clock) used for synchronized performance of a plurality of instruments (e.g., sequencer and rhythm machine), the start message, the stop message and the continue (continuous start) message. The MIDI clock is transmitted every 1/24th of a quarter note (ninety-sixth note) and each instrument measures the time based upon this clock for the performance.

The MIDI clock controller of the YM3523 is provided to attain the following purposes with respect to the messages: attain the following purposes with respect to the messages:

- Automatic control of the counters and SYNC output circuits synchronized with the reception of the clock message and the tape SYNC signal, or the clock message transmission.

- The speedup of the CPU response to the reception of the system real-time message.

- The priority transmission of the system real-time message and automatic transmission of some of the system real-time message.

- The generation of the internal MIDI clock triggered by the reception of the clock message, the tape SYNC signal, the internal timer, or by the host CPU operation, and subsequent IRQ generation.

- The concurrent control of the counters, the output circuit and the message transmission, all of which synchronized with the internal MIDI clock.

- The guarantee of the process sequence of the clock message and other system real-time messages when the reception of the clock message is used as a trigger for the internal MIDI clock.

#### 4.1.2. SYNC detector