# V9938 MSX-VIDEO Technical Data Book

ASCII CORPORATION/NIPPON GAKKI CO., LTD.

#### PREFACE

The V9938 introduced in this manual is a Very Large-Scale Integrated Circuit (VLSI) that was developed as a Video Display Processor (VDP) for the MSX2. The MSX personal computer standard was introduced in 1983 by ASCII Corporation and Microsoft Incorporated. At present, the MSX is manufactured and marketed worldwide. In 1985, out of the desire to strengthen some of the functions of the original MSX, the MSX2 standard was developed. In addition to being software-compatible with the MSX, the MSX2 supports new media and has video processing capabilities that are not available on conventional 8-bit personal computers.

To make the MSX2 a reality, two requirements for the Video Processor were upward compatiblity with the existing TMS9918A (the VDP for the MSX) software while increasing the number of functions. The V9938 was developed through the joint efforts of ASCII Corporation, Microsoft Incorporated, and YAMAHA.

The following functions are supported on the V9938.

- Full bit-mapped mode

- 80-column text display

- Access using X- and Y-coordinates. The load of the I/O driver has been lightened. The X-Y coordinates are independent of the screen mode.

- fundamental commands implemented by hardware to decrease the processing time of the I/O driver: AREA MOVE, LINE, SEARCH, RASTER OPERATION, etc.

- Digitize and external synchronization Color palette (9 bits x 16 patterns)

- Linear RG8 video output

468806800000

- More sprites per horizonatal line

Because the V9938 has the above functions, it provides for superior video capabilities that make it possible for its use in a variety of applications, including the MSX2. CAPTAIN terminals and NAPLPS terminals using the V9938 have already been developed. We hope that the V9938 will be a standard video processing device on a worldwide

This manual was written so as to explain how to set the parameters of the V9938 and is a reference for developing applications and systems software for it.

We are pleased that you have chosen to develop software for the V9938 and that you have referred to this manual for assistance.

Pinally, we would like to express our deep gratitude to the people at NTT as well as the other related manufacturers for their valuable opinions which contributed to the development of the V9938.

> August, 1985 ASCII Corporation

# CONTENTS

# PART 1 MSX-VIDEO DATA PROCESSOR V9938 USER'S MANUAL

| BASIC INPUT AND OUTPUT                                                                        |

|-----------------------------------------------------------------------------------------------|

| 1. Accessing the Control Registers 1                                                          |

| 2. Accessing the Pallete Registers 1                                                          |

| 3. Accessing the Status Registers 2                                                           |

| 4. Accessing the Video RAM 2                                                                  |

|                                                                                               |

| REGISTER FUNCTIONS 4                                                                          |

| 1. CONTROL REGISTERS #0 to #23 (Write only) 4                                                 |

| 2. STATUS REGISTERS #0 to #9 (Read only)9                                                     |

| TEXT 1 MODE                                                                                   |

|                                                                                               |

| TEXT 2 MODE                                                                                   |

| MULTICOLOR HODE 20                                                                            |

| GRAPHIC 1 MODE                                                                                |

| GRAPHIC 2 AND GRAPHIC 3 MODES                                                                 |

| GRAPHIC 4 MODE                                                                                |

| GRAPHIC 5 MODE41                                                                              |

| GRAPHIC 6 MODE 46                                                                             |

| GRAPHIC 7 MODE 50                                                                             |

| ######################################                                                        |

| COMMANDS54                                                                                    |

| 1. Types of Commands 54                                                                       |

| 2. Page Concept55                                                                             |

| 3. Logical Operations 56                                                                      |

| 4. Explanations of Commands 57                                                                |

| 4.1 HMMC (High-speed move CPU to VRAM)                                                        |

| 4.2 YMMM (High-speed move VRAM to VRAM, y only) 60 4.3 HMMM (High-speed move VRAM to VRAM) 62 |

| 4.4 HMMV (High-speed move VDP to VRAM)                                                        |

| 4.5 LMMC (Logical move CPU to VRAM)                                                           |

| 4.7 LMMM (Logical move VRAM to VRAM)                                                          |

| 4.8 LMMV (Logical move VDP to VRAM)                                                           |

| 4.9 LIRE 76                                                                                   |

| 4.11 PSET                                                                                     |

| 4.12 POINT                                                                                    |

ordes o

| 5.      | Speeding up the processing of commands           | 64  |

|---------|--------------------------------------------------|-----|

| 6.      | Conditions of registers after command execution  | 85  |

|         |                                                  |     |

| SPRITES | 3                                                | 86  |

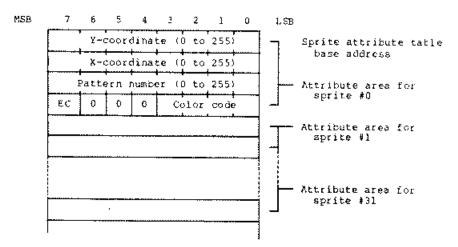

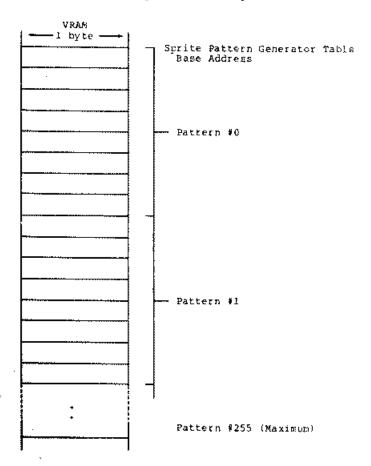

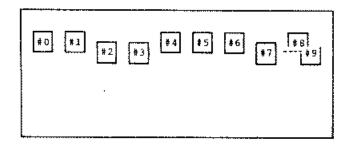

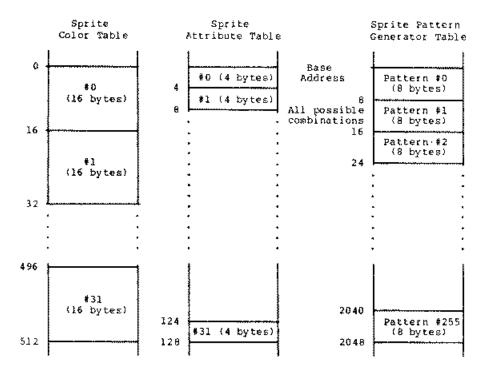

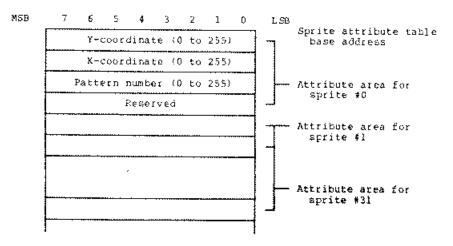

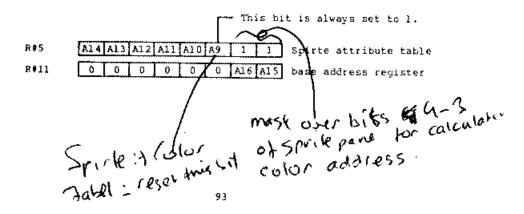

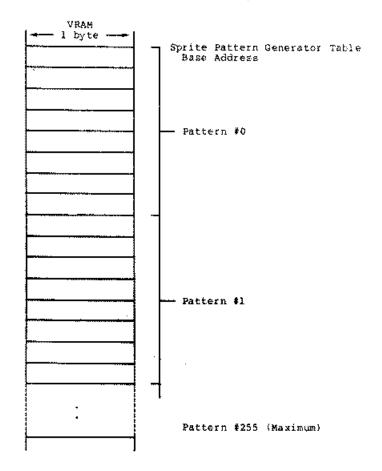

| 1.      | SPRITE MODE 1 (G1, G2, MC)                       | 87  |

| 2.      | SPRITE MODE 2 (G3, G4, G5, G6, G7)               | 91  |

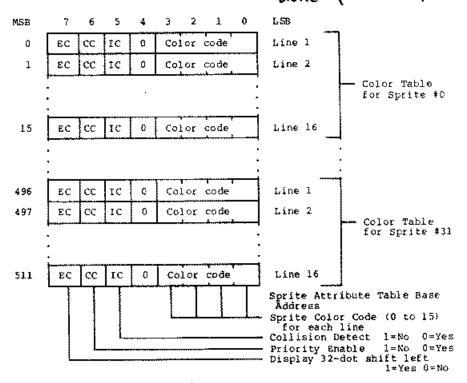

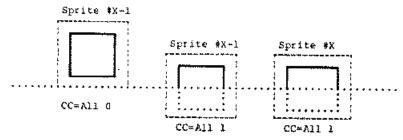

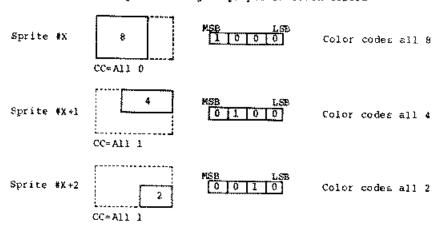

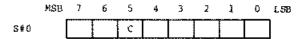

| 3.      | Setting the Sprite Colors                        | 9.8 |

|         |                                                  |     |

| POINTI  | NG DEVICES                                       | 99  |

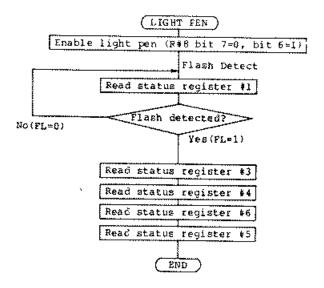

| ı.      | Light pen                                        | 99  |

| 2.      | Mouse 1                                          | 01  |

|         |                                                  |     |

| SPECIA  | L FUNCTIONS                                      | 02  |

| 1.      | Alternate display of two graphics screen pages I |     |

| 2.      | Interlace display 1                              | .03 |

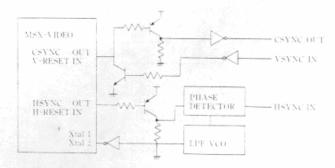

| 3.      | External Synchronization 1                       |     |

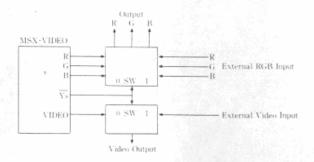

| 4.      | Superimpose                                      | 105 |

| 5.      | Digitize function                                | 06  |

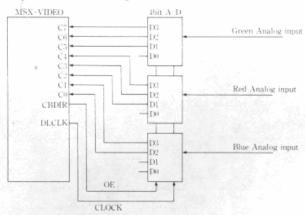

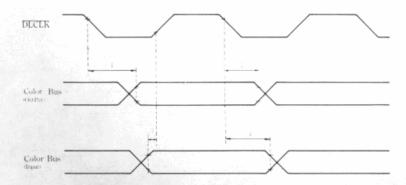

| 6.      | Color bus                                        | 109 |

· · · · · · · · ·

# PART 2 MSX-VIDEO DATA PROCESSOR LSI DATA SHEET

| 1. | 1400                                                             | -Vipeo,                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|----|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 1. | MD A                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

|    | 1-1                                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                        | 111                                                                       |

|    | 1-2                                                              | Peatures                                                                                                                                                                                                                                                                                                                                                                                                                        | 111                                                                       |

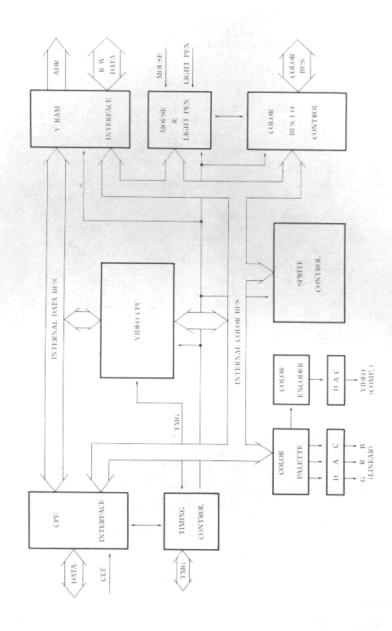

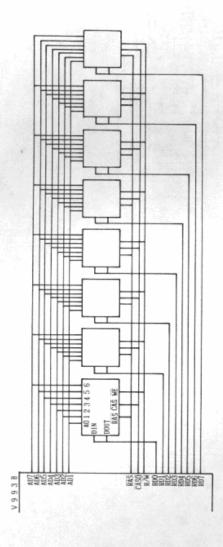

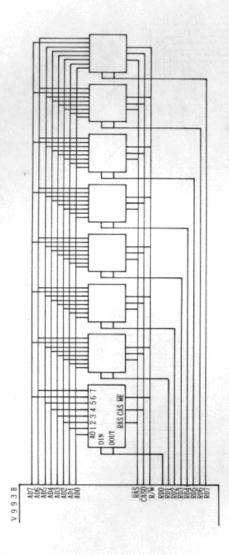

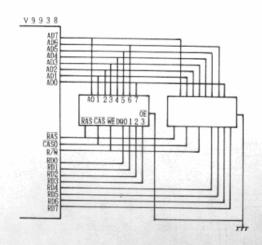

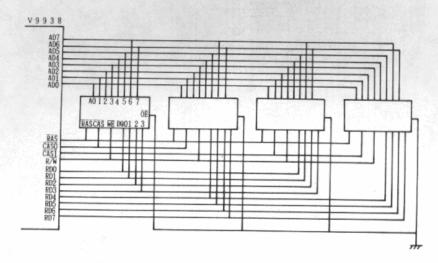

|    | 1-3                                                              | MSX-VIDEO Block diagram                                                                                                                                                                                                                                                                                                                                                                                                         | 112                                                                       |

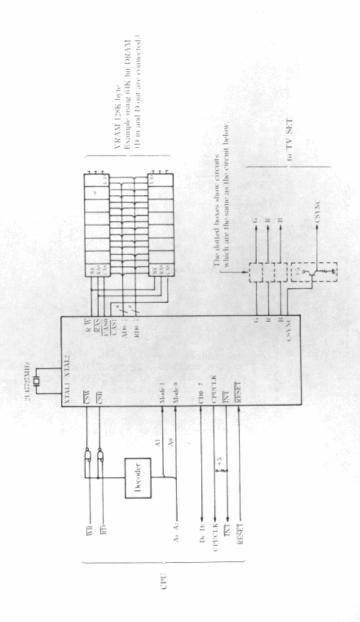

|    | 1-4                                                              | MSX-VIDEO circuit example                                                                                                                                                                                                                                                                                                                                                                                                       | 113                                                                       |

| 2. | Pin                                                              | assignments and functions                                                                                                                                                                                                                                                                                                                                                                                                       | 114                                                                       |

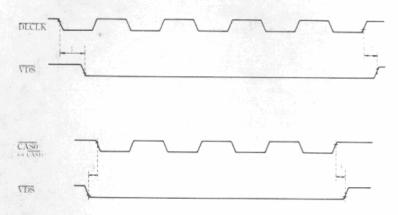

| з. | £le                                                              | ctrical characteristics and timing chart                                                                                                                                                                                                                                                                                                                                                                                        | 116                                                                       |

|    | 3-1                                                              | Absolute maximum ratings                                                                                                                                                                                                                                                                                                                                                                                                        | 116                                                                       |

|    | 3-2                                                              | Recommended operating conditions                                                                                                                                                                                                                                                                                                                                                                                                | 116                                                                       |

|    | 3-3                                                              | Electrical characteristics under recommended operating conditions                                                                                                                                                                                                                                                                                                                                                               | 117                                                                       |

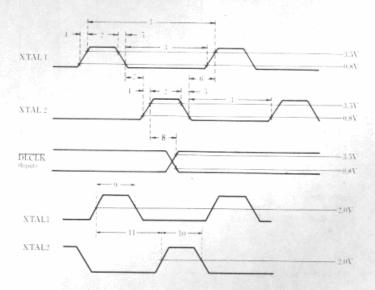

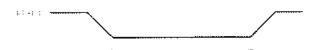

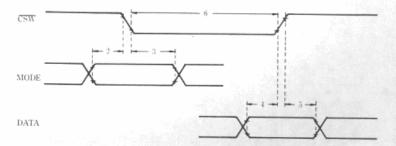

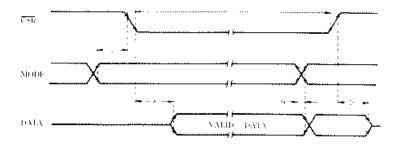

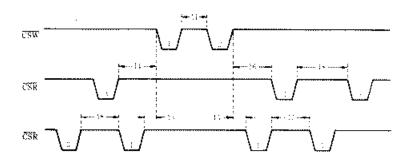

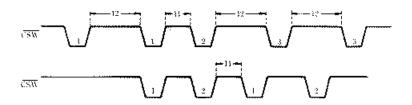

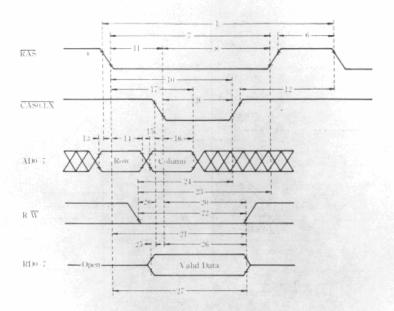

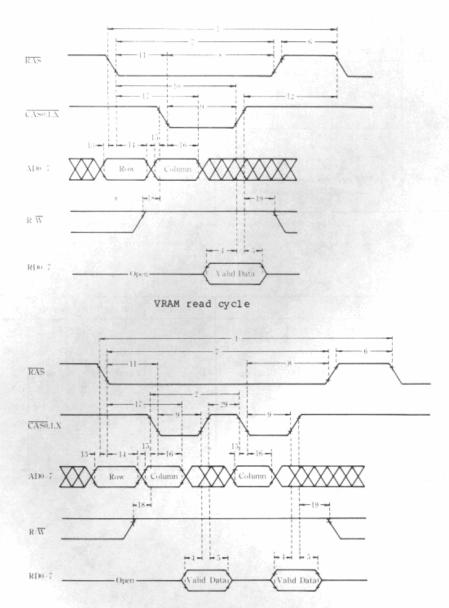

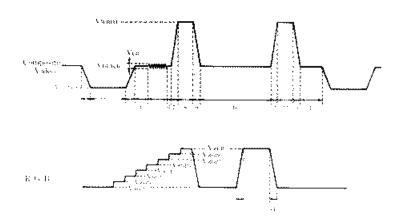

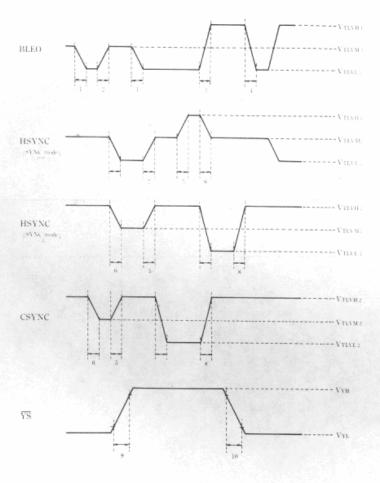

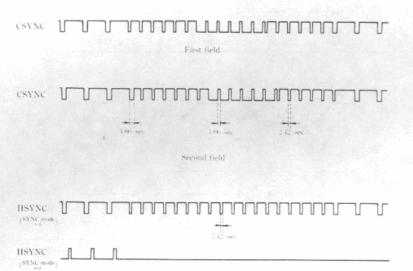

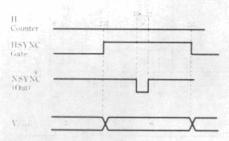

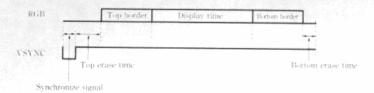

|    | *R<br>DC<br>In<br>Ex<br>CP<br>MS<br>Cor<br>RG<br>Sy<br>Cor<br>RG | ternal input clock timing.  ESET Input timing.  characteristics.  put/output power capacities.  ternal output clock timing.  U-MSX-VIDEO Interface.  X-VIDEO-VRAM interface.  mposite video signal output level.  nchronize signal output level.  signal.  nchronize signal.  Inchronize signals.  Inchronize signals.  Inchronize signals.  Inchronize signals.  Inchronize signals.  Inchronize signals.  Inchronize signals. | 118<br>118<br>119<br>121<br>123<br>126<br>127<br>128<br>128<br>129<br>132 |

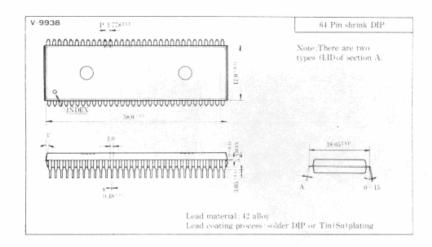

|    | 4, E                                                             | xternal measurements of package                                                                                                                                                                                                                                                                                                                                                                                                 | 1.34                                                                      |

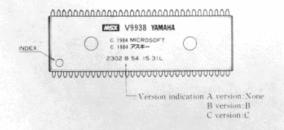

|    | 5. V                                                             | ersion identification]                                                                                                                                                                                                                                                                                                                                                                                                          | 134                                                                       |

# APPENDIX

| ì.  | Refresh                              | 135  |

|-----|--------------------------------------|------|

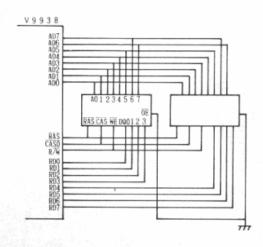

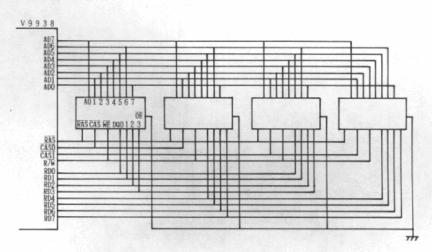

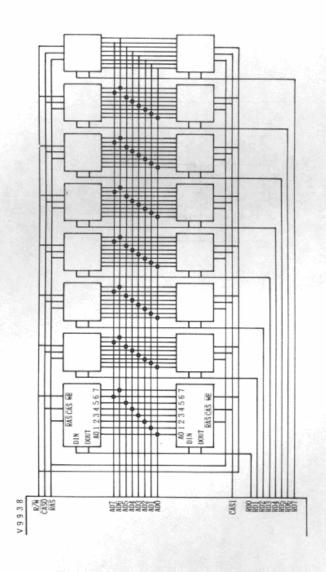

| 2,  | Examples of VRAM Interface           | 137  |

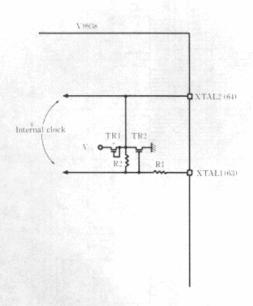

| З.  | Clock oscillation internal circuitry | 1 42 |

| 4.  | Usage of unused pins                 | 1 43 |

| ۶.  | Cycle mode                           | 1.44 |

| 6.  | Cycle input                          | 1 45 |

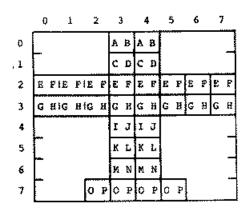

| 7.  | Display parameters                   | 146  |

| 8,  | Color palette                        | 148  |

| 9.  | Composite video color burst          | 149  |

| 10, | Color bus                            | 130  |

| 11. | Sprites in GS mode                   | 151  |

# PART 1

# MSX-VIDEO DATA PROCESSOR V9938 USER'S MANUAL

BASIC INPUT AND OUTPUT

# 1. Accessing the Control Registers

There are two ways to set data in the MSX-VIDEO control registers (R#D to R#46), which we will describe below.

#### 1.1 Direct access

Output the data and the register number in sequence to port \$1. Since this order is always used, be careful when you access the MSX-VID£O for an interrupt routine.

| MSB                | 7 | 6  | 5  | 4  | 3  | 2  | 1  | 0  | LSB      |   |

|--------------------|---|----|----|----|----|----|----|----|----------|---|

| Port #1 First byte |   | อ6 | 5۵ | D4 | Þ3 | D2 | D1 | ₽Đ | DATA     |   |

| Second by te       | 1 | D  |    |    |    | R2 |    | RÖ | REGISTER | # |

#### 1.2 Indirect access

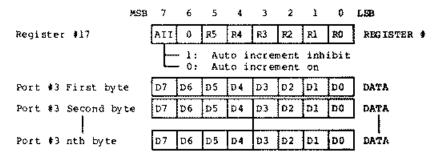

Specify the register number in control register R#17 (Control Register Pointer).

First set the register number in R#17 (using direct addressing) by sending data to Port #3. When you set the data in R#17, you can also set its MSB (A11, the autoincrement bit) to control autoincrementing. The data in R#17 cannot be changed by indirect addressing.

If autoincrementing is prohibited, the contents of R#17 will be unchanged, and thus you do not have to reset R#17.

# 2. Accessing the Pallete Registers

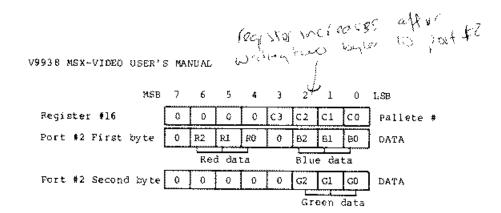

To set data in the MSX-VIDEO palette registers (P#O to P#15/9 bit), you must first set the palette register number in register R#16 (Color palette address pointer) and subsequently output the two bytes of data (in order) through port #2.

# 3. Accessing the Status Registers

To read the status registers of the MSX-VIDRO (S#0 to S#9), you must first set the register number in R#15 (Status register pointer) and read the data through Port #1.

| MS                | В 7 | 6  | 5  | 4  | 3  | 2  | 1  | 0   | LSB    |          |   |

|-------------------|-----|----|----|----|----|----|----|-----|--------|----------|---|

| Register #15      | G   | G  | 0  | 0  | s3 | 52 | Sl | \$0 | Status | register | Ħ |

| Port #1 Read data | ₽7  | D6 | DS | D4 | D3 | D2 | D1 | DΟ  | DATA   |          |   |

#### 4. Accessing the Video RAM

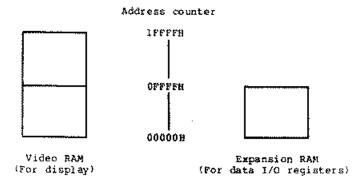

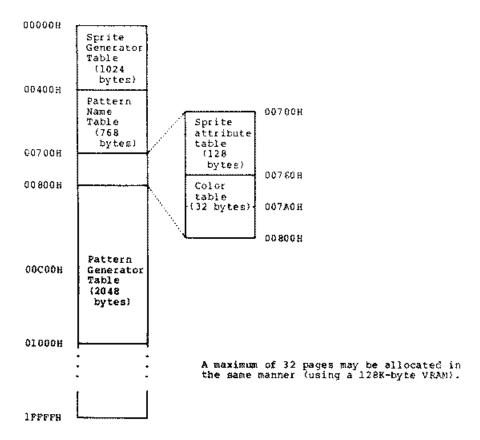

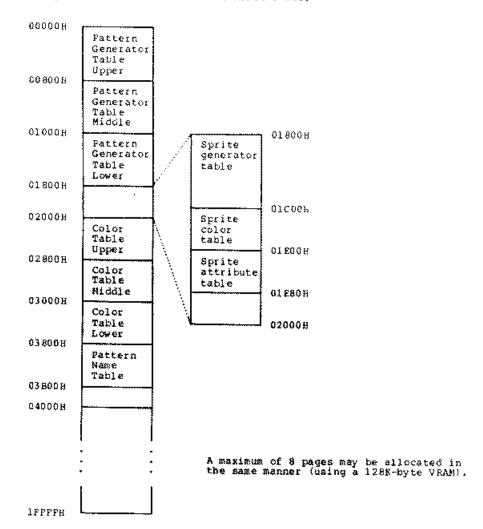

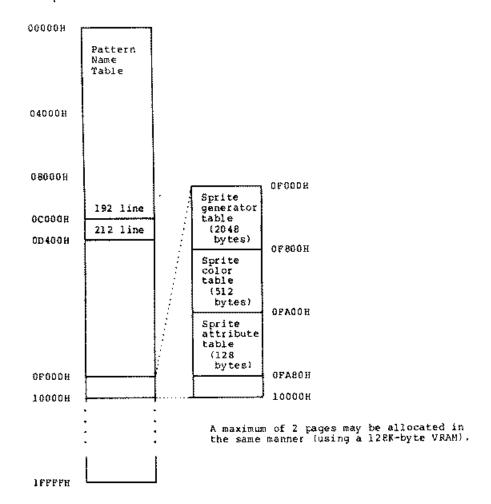

A Video RAM of 128K bytes plus an expansion RAM of 64K bytes can be connected to the MSX-VIDEO. The memory maps for these cases are shown in the map below.

# Accessing memory

To access memory, follow the procedure below.

- Switch banks (VRAM to Expansion RAM)

Set the address counter (A16 to A14)

Set the address counter (A7 to A0)

- Set the address counter (Al3 to A8), and specify read or write

Read or write the data

1. Switching banks (VRAN to Expansion RAM)

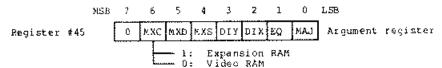

Since the contents of R#45 (Argument register) do not change each time that memory is accessed, it is not necessary to respecify bit 6 of register R#45 (which specifies banking) every time that you are to do banking.

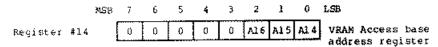

Setting the address counter (A16-A14)

Set the high-order three bits (Al6 to Al4) of the address counter using register R#14 (VRAM Access base address register).

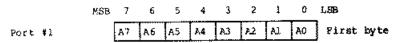

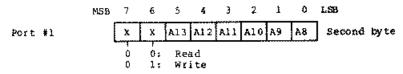

Setting the address counter (A7 to A0)

Set the low-order eight bits (A7 to A0) of the address counter by outputting data to Port #1.

4. Setting the address counter (Al3 to A8) and specifying read or write

Set the remaining six bits (Al3 to A8) of the address counter and specify read or write by outputting data to Port #1.

5. Reading or writing data

Since the address counter is automatically incremented when data is read from or written to Port #0, you may continually access blocks of data.

- \* To access the VRAN, you can also use commands. These commands will

- be explained in a later chapter.

\* Refer to the data sheet for access timings.

· ........

#### REGISTER FUNCTIONS

1. CONTROL REGISTERS #0 to #23 (Write only) \*32 to #46 (Write only)

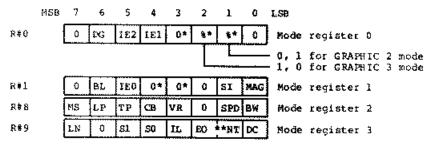

# 1.1 Mode Registers

|     | MSB | _ <sup>7</sup> | 6   | 5   | 4   | 3  | 2    | 1   | O   | LSB  |          |   |

|-----|-----|----------------|-----|-----|-----|----|------|-----|-----|------|----------|---|

| R#O |     | 0              | DG  | IE2 | ĪEI | М5 | M4 / | жЗ  | 0   | Mode | Register | e |

| R#1 |     | C              | BL  | IEO | ыј  | ₩2 | Ó    | si  | MAG | Mode | Register | 1 |

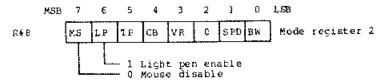

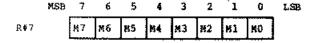

| R#8 |     | MS             | Ľ.Þ | ΤP  | СВ  | ٧R | 0    | SPD | BW  | Mode | Register | 2 |

| R#9 |     | LN             | 0   | Sl  | S0  | ĭĿ | ĖO   | *NT | DC  | Mode | Register | 3 |

\* Indicates negative logic.

R#0 DG : Sets the color bus to input mode, and inputs data into the VRAM.

IS2: Enables interrupt from Lightpen by Interrupt Enable 2.

IEl: Enables interrupt from Morizontal scanning line by

Interrupt Enable 1.

M5 : Used to change the display mode. M4: Dised to change the display mode. M3: Dised to change the display mode.

BL : When 1, screen display enabled. When 0, screen disabled.

IEO: Enables interrupt from Horizontal scanning line by

Interrupt Enable 0.

Used to change the display mode. Used to change the display mode.

SI: When 1, sprite size is 16 x 15. When 0, 8 x 8. MA: Sprite expansion; when 1: expanded. When 0, normal.

R#8 MS : When 1, sets the color bus to input mode and enables mouse. When 0, sets the color bus to output mode and disables

when 1, enables light pen. When 0, disables light pen. Sets the color of code 0 to the color of the palette. TP ;

CB:

When 1, sets the color bus to input mode. When 0, sets the color bus to output mode. Selects the type of Video RAM.

Selects the type of video knm.

1 = 64K x 1 bit or 64K x 4 bits.

0 = 16K x 1 bit or 16K x 4 bits.

When 1, disables display of sprite. When 0, displays SPD:

sprite.

When 1, sets black and white in 32 tones. When 0, sets color (available only with a composite encoder).

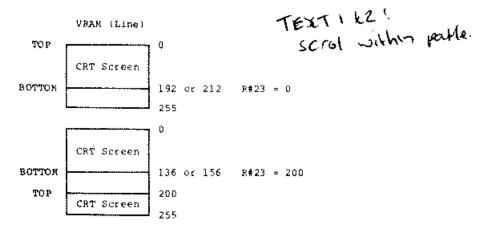

R#9 LN : When 1, sets the horizontal dot count to 212. When 0, sets the horizontal dot count to 192. S1 : Selects simultaneous mode. S0 : Selects simultaneous mode.

TL: When I, interlace (Complete NTSC timing)

When 0, non-interlace (Incomplete NTSC timing) When 1, displays two graphic screens interchangably by Even field/Odd field.

When 0, displays the same graphic screen by Even

field/Odd field.

\*NT: When 1, PAL (313 lines); when 0, NTSC (262 lines).

(For RGR output only)

DC : When 1, sets \*DLCLK to input mode; when 0, sets \*DLCLK to output mode.

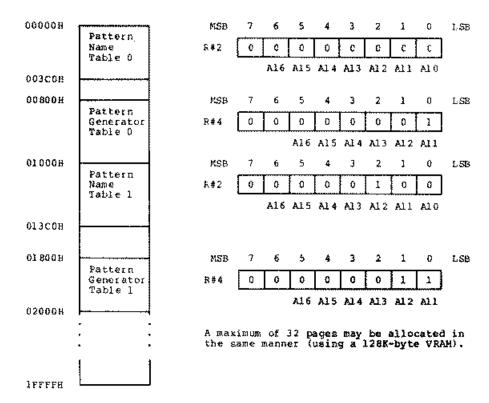

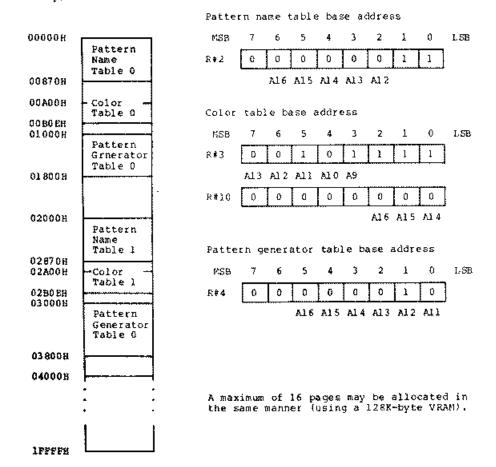

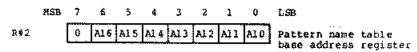

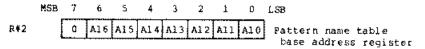

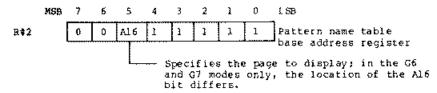

# 1.2 Table Base Address Registers

The table base address registers are a set of registers to declare the addresses of tables in the VRAM to be used by MSX-VIDEO.

Note that when these registers are accessed, the control codes that the screen may receive depends on the display mode. For this purpose, you must mask the unwanted bits.

|     | MSB | 7    | 6    | 5           | 4    | 3    | 2    | 1    | 0          | LSB                                                  |

|-----|-----|------|------|-------------|------|------|------|------|------------|------------------------------------------------------|

| R#2 |     | 0    | A16  | <b>A</b> 15 | A1 4 | A13  | A1 2 | AlI  | Alc        | Pattern name table base<br>address register          |

| R#3 |     | Al 3 | A1 2 | All         | AL 0 | А9   | ВА   | A7   | A6         | Color table base address<br>register low             |

| R#1 | 0   | a    | Q    | 0           | Đ    | Đ    | Al 5 | A15  | Al 4       | Color table base address<br>register high            |

| R#4 |     | 0    | 0    | VJ 6        | λ15  | A1 4 | A13  | Al 2 | A11        | Pattern generator table<br>base address register     |

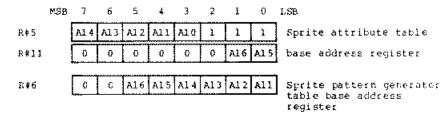

| R#5 |     | Al 4 | Al 3 | A1 2        | All  | A1 0 | A9   | 8A   | <b>A</b> 7 | Sprite attribute table base address register low     |

| R#1 | 1   | 0    | 0    | 0           | Ç    | 0    | 0    | Al6  | Al 5       | Sprite attribute table base address register high    |

| R#6 |     | ņ    | 0    | A16         | A15  | A1 4 | Aì 3 | Al 2 | All        | Sprite pattern generator table base address register |

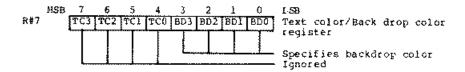

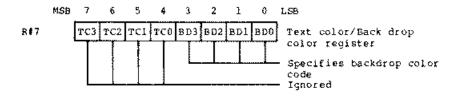

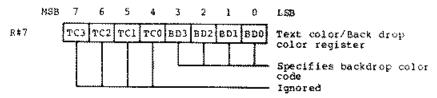

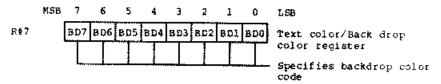

# 1.3 Color Registers

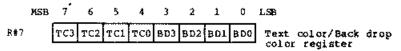

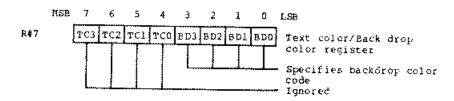

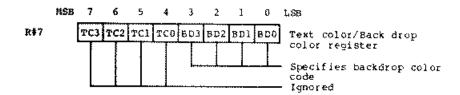

The color registers are used to control the MSX-VIDEO's text and background screen colors as well as blinking, etc.

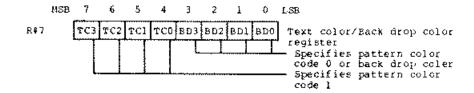

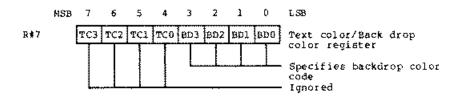

TC3 to TC0: Specifies the text color according to TEXT 1 and TEXT 2 modes.

BD3 to BD0: Specifies the back drop color in all display modes.

MSB 7 6 5 4 3 2 1 0 LSB

R#12 T23 T22 T21 T20 BC3 BC2 BC1 BC0 Text color/Back calor register

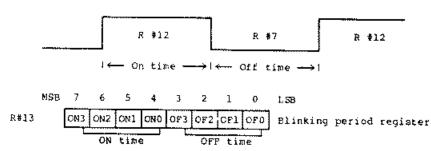

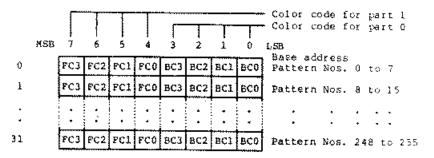

In TEXT 2 mode, if the attributes for blinking are set, the color set in this register and set in R#7 are displayed alternately.

T23 to T26: Specifies the color of part 1 of the pattern. BC3 to BC0: Specifies the color of part 0 of the pattern.

In the bit map modes of GRAFH4 to GRAFH7, the two pages are alternately displayed (blinked). Place data in this register to set the display page to an odd page to begin blinking. This register is also used in the TEXT2 mode.

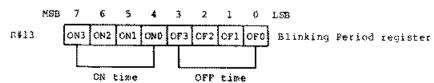

ON3 to ON0: Display time for even page OF3 to OF0: Display time for odd page

MSB 7 6 5 4 3 2 1 0 LSB R#20 0 C 0 Ċ Ď 0 0 0 Color burst register 1 R#21 0 0 1 1 1 0 1 Color burst register 2 1 R#22 0 0 Đ 0 0 O 1 Color burst register 3 1

The above values are preset when the power is applied. If all values in the above three registers are set to 0, the color burst signal of the composite video output will be erased.

If the above values are subsequently reset to the preset values, the normal color burst signal will be output.

#### 1.4 Display Registers

The display registers are used to control the display position on the CRT.

M58 7 6 5 3 2 1 0 LSB V3 R#18 VZ V1 ۷Ø H3 **E2** Hl Display adjust register

The above register is used to adjust the display position on the CRT.

H = 7 . . . H = 1, H = 0, H = 15 . . . H = 8 (Left) (Center) (Right)

V = 8 , . . V = 15, V = 0, V = 1 . . . V = 7 (Bottom) (Center) (Top)

MSB 7 6 5 4 3 2 1 0 LSB

R#23 DO7 DO6 DO5 DO4 DO3 DO2 DO1 DO0 Display offset register

The above register sets the location of the line to begin display.

MSB 7 6 5 4 3 2 1 0 LSB

R#19 | IL7 | IL6 | IL5 | XL4 | IL3 | IL2 | IL1 | IL0 | Interrupt line register

You may specify interrupts when the MSX-VIDEO begins to display a specified scanning line. To enable the interrupt, use the above register to set the scanning line.

#### 1.5 ACCESS REGISTERS

The access registers are a set of registers used when accessing the MSX-VIDEO registers or the VRAM.

MSB 7 6 5 4 3 2 1 0 LSB

R#14 0 0 0 0 0 Al6 Al5 Al4 VRAM Access base address

When accessing the MSX-VIDEO and the Video RAW (VRAM), set the highorder three blts of the address in the VRAM access base address register.

When data is set in this register, and the VRAM is accessed, if there is a carry from All, the data in the register is automatically incremented. In GRAPHIC1, GRAPHIC2, MULTICOLOR, and TEXTI modes, the data in the register is not automatically incremented.

R#15 0 0 0 0 83 82 81 80 Status register pointer

When reading the MSX-VIDEO status registers (S#O to S#9), set the contents of the Status register pointer.

| MSB  | 7 | 6 |   |   | -   | _  | 1  | 0  | I-SB  |         |         |

|------|---|---|---|---|-----|----|----|----|-------|---------|---------|

| R#16 | Ó | 0 | 0 | Q | C 3 | C2 | C1 | СŮ | Color | palette | address |

When setting the color palette of the MSX-VIDEO, set the number of the palette in the Color palette address register.

| MSB  | 7   | 6 | 5   | 4   | 3   | 2   | I   | O   | LSB     |          |         |

|------|-----|---|-----|-----|-----|-----|-----|-----|---------|----------|---------|

| R#17 | AĭI | 0 | RS5 | RS4 | RS3 | RS2 | RS1 | RS0 | Control | tegister | pointer |

In the MSX-VIDEO, the above control register pointer may be used to access another register. In addition, according to the setting of the AII bit, the data can be automatically incremented.

AII = 1: Auto increment disabled AII = 0: Auto increment enabled

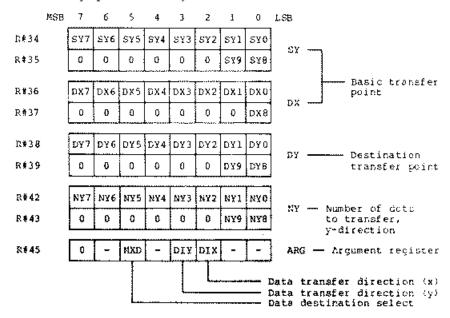

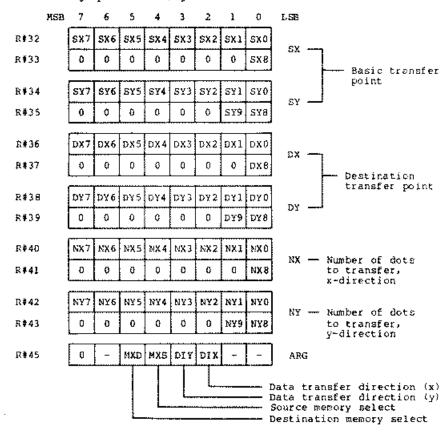

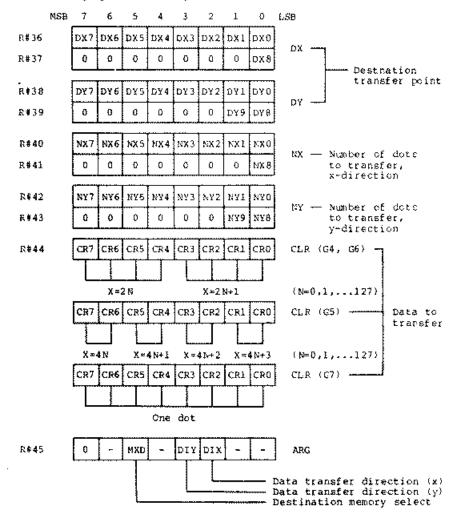

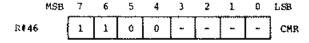

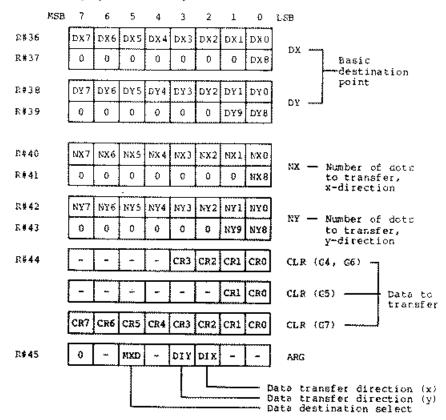

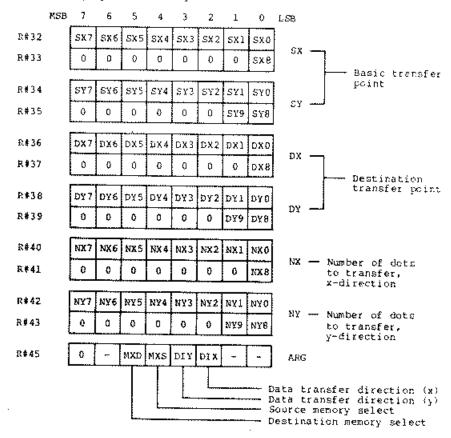

# 1.6 COMMAND REGISTERS

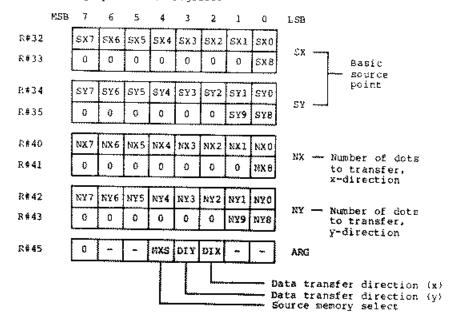

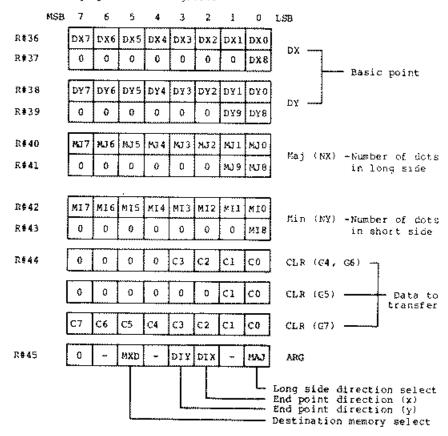

The following command registers are used when executing a command on the MSX-VIDEO. Details on the use of these command registers will be presented in a later chapter.

| ask  | 7   | 6            | 5   | 4   | 3           | 2   | 1   | 0    | LSB                            |

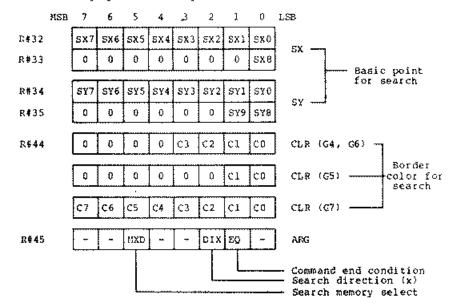

|------|-----|--------------|-----|-----|-------------|-----|-----|------|--------------------------------|

| R#32 | SX7 | 8 <b>X</b> 6 | SX5 | SX4 | sx3         | sx2 | SXI | SXO  | Source X low register          |

| R#33 | 0   | 0            | 0   | 0   | 0           | D   | ٥   | SX8  | Source X high register         |

| R#34 | SY7 | SY6          | SY5 | SY4 | 5¥3         | SY2 | SYl | SYO  | Source Y low register          |

| R#35 | 0   | Q            | 0   | Ó   | 0           | 0   | SY9 | SY8  | Source Y high register         |

| 1    |     | ş            |     |     | <del></del> |     |     |      |                                |

| R#36 | DX7 | DX6          | DX5 | DX4 | EXG.        | DX2 | DX1 | OXO  | Destination X low register     |

| R#37 | 0   | 0            | 0   | 0   | 0           | 0   | 0   | DX8  | Destination % high register    |

| 8E#Я | DY7 | DY6          | DY5 | DY4 | DY3         | DY2 | נצם | DYO  | Destination Y low register     |

| R#39 | Q.  | 0            | 0   | 0   | 0           | 0   | D¥9 | DY 6 | Destination Y high register    |

|      |     | ····         |     | ,   |             |     |     |      |                                |

| R#40 | NX7 | NX6          | NX5 | NX4 | NX3         | NXZ | NXI | NXÖ  | Number of dots X low register  |

| R#41 | D   | Đ            | 0   | 0   | 0           | 0   | 0   | ВХИ  | Number of dots X high register |

| R#42 | NY7 | NYБ          | NY5 | NY4 | күз         | NY2 | NY1 | NY 0 | Number of dots Y low register  |

| R#43 | 0   | 0            | 0   | 0   | 0           | 0   | NY9 | NYB  | Number of dots Y high register |

|      |     |              |     |     |             |     |     |      |                                |

| R#44 | CH3 | CH2          | CH1 | CH0 | СЦ3         | CL2 | CL1 | CLO  | Color register                 |

| R#45 | 0   | MXC          | MXD | MXS | D1 Y        | DIX | EQ  | MAJ  | Argument register              |

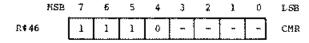

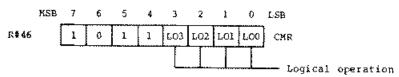

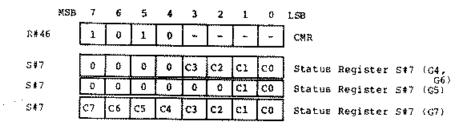

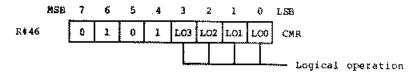

| R#46 | смз | CM2          | CMl | смо | LO3         | L02 | LOl | L00  | Command register               |

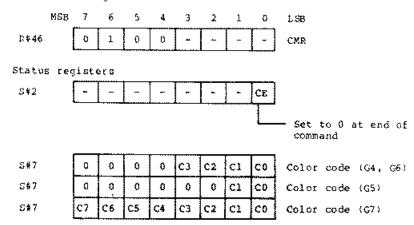

#### 2. STATUS REGISTERS #0 to #9 (Read only)

The following status registers are read-only registers for reporting the status when the MSX-VIDEO is read.

| MSB | 7 | 6             | 5  | 4 | 3 | 5           | 1           | 0 | LSB |  |

|-----|---|---------------|----|---|---|-------------|-------------|---|-----|--|

| - 1 |   | $\overline{}$ | TT |   |   | <del></del> | <del></del> |   | 1   |  |

When S#O is read, this flag is reset.

- S#0 F 5S C Fifth sprite number Status register 0

F: Vertical scanning interrupt flag

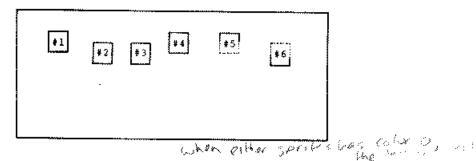

- 55: Flag for the fifth sprite Five sprites are aligned on the first horizontal line (In the G3 to G7 modes, 9 sprites are allowed)

- C: Collision flag Two sprites have collided.

Fifth sprite number:

The number of the fifth (or minth) sprite.

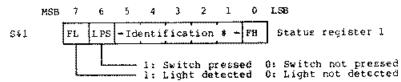

MSB 7 6 5 4 3 2 1 0 LSB

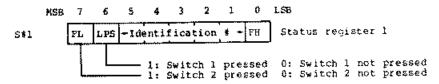

S#1 FL LPS Identification # FH Status register 1

FL: Lightpen flag (Lightpen flag set)

If the lightpen is to detect light, this bit as well as the IE2 bit must be both set in order for an interrupt to be enabled. When S#1 is read, FL is reset.

Mouse switch 2 (Mouse flag set)

The second switch on the mouse was pressed.

In this case, when S#l is read, FL is not reset.

LPS: Lightpen switch (Lightpen flag set)

The lightpen switch was pressed.

In this case, when S#1 is read, LPS is not reset.

Mouse switch 1 (Mouse flag set)

The first switch on the mouse was pressed.

In this case, when S#1 is read, LPS is not reset.

Identification number:

The identification number (ID \*) of the MSX-VIDEO.

FH: Rorizontal scanning interrupt flag

Horizontal scanning interrupt (which is specified in R#19)

flag. If IEl is set, an interrupt is enabled. When S#1

is read, FH is reset.

MSB 7 6 5 4 3 2 1 0 LSB

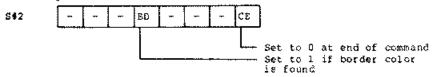

S#2 TR VR HR BD 1 1 EO CE Status register 2

TR: Transfer ready flag

When the CPU sends commands to the VRAM and other devices,

the CPU checks this flag while transferring data. When this

flag is set to 1, transfer may be done.

Valant

UR reset

Set during Valant of Paraer

V9938 MSX-VIDEO USER'S MANUAL

VR: Vertical scanning line timing flag puring vertical scanning, this flag is set to 1.

HR: Horizontal scanning line timing flag & Set durny Holank

During horizontal scanning, this flag is set to 1.

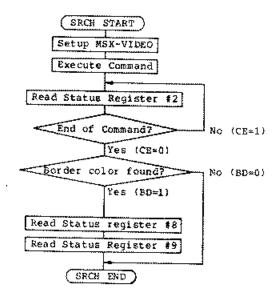

BD: Boundary color detect flag

When the search command is executed, this flag detects

whether the boundary color was detected or not.

EG: Display field flag

When 0. indicates the first field.

When 1. indicates the second field.

CE: Command execution flag Indicates that a command is being executed.

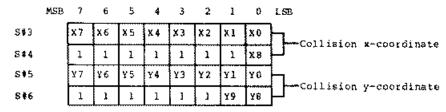

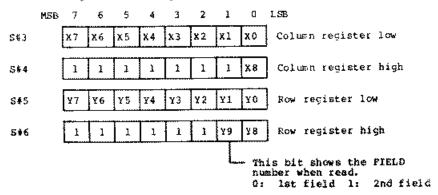

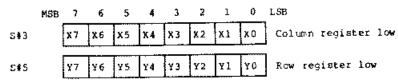

| MSB          | 7  | 6.  | 5  | 4  | 3  | 2  | 1  | 0  | I.SB                 |

|--------------|----|-----|----|----|----|----|----|----|----------------------|

| \$#3         | Х7 | Х6  | хs | X4 | ХЗ | Х2 | XI | ХO | Column register low  |

| S#4          | 1  | 1   | 1  | 1  | 1  | 1  | 1  | ХB | Column register high |

| S <b>‡</b> 5 | ¥7 | Y 6 | ¥5 | ¥4 | Y3 | Y2 | Yl | ΥO | Row register low     |

| S#6          | 1  | ı   | 1  | 1  | ì  | 1  | ΕQ | ¥θ | Row register high    |

The above registers are set to indicate the collision location of sprites, the location of lightpen detection, and the relative movement of the mouse.

|                |    |    | _  |    | _  |    |    |    |       |          |

|----------------|----|----|----|----|----|----|----|----|-------|----------|

| \$ <b>\$</b> 7 | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 | Color | register |

The above color register is used when the POINT and VRAM to CPU commands are executed. The VRAM data is set in this register.

| S#8 | BX7 | вхб | вх5 | BX4 | вхэ | BX2 | BXl | BX0 | Borđer | x | register | Low  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------|---|----------|------|

| 5#9 | 1   | 1   | ī   | 1   | 1   | 1   | 1   | вха | Border | х | register | hiah |

When the search command is executed and the border color has been detected, the X coordinate is set in the above registers.

# TEXT 1 MODE

#### Characteristics

- Pattern size ; 6 dots (w) x 8 dots (h) - Patterns : 256 types

- Screen pattern count : 40 (w) x 24 (h) patterns

- Pattern colors : Two colors out of 512 colors (per screen)

- VRAM area per screen : 4K bytes

# Controls

- Pattern font : VRAM pattern generator table - Screen pattern location : VRAN pattern name table - Pattern color code 1 : High-order four bits of R#7

- Pattern color code 0 : Low-order four bits of R#7

- Background color code : Low-order four bits of R#7

#### Initial Settings

#### 1. Mode and Register Settings

|     | MSB | 7  | 6  | 5   | 4   | 3   | 2    | ì   | 0   | L58  |          |   |

|-----|-----|----|----|-----|-----|-----|------|-----|-----|------|----------|---|

| R#0 |     | 0  | DG | IE2 | IE1 | D*  | Ç*   | 0*  | 0   | Mode | register | 0 |

| R#1 |     | 0  | BL | 1E0 | 1*  | Đ*  | 0    | sī  | MAG | Mode | register | 1 |

| R#5 |     | MS | LP | ΤP  | CB  | ٧R  | 0    | SPD | BW  | Mode | register | 2 |

| R#9 |     | LN | Q. | Sl  | SÜ  | 11, | £0 1 | *NT | DC  | Mode | register | 3 |

Examples of settings in TEXT 1 mode

\*\* Indicates negative logic All other bits are set accordingly

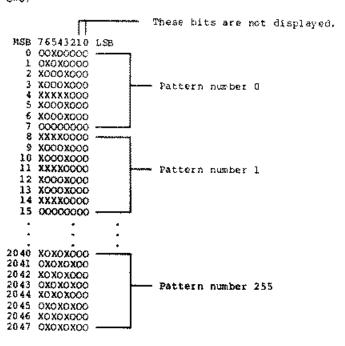

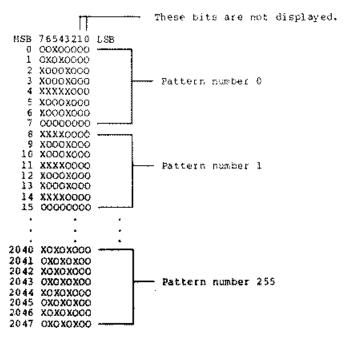

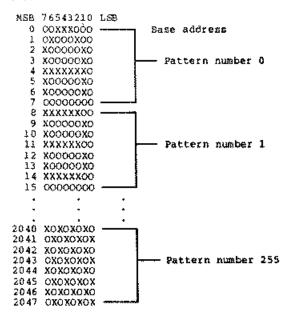

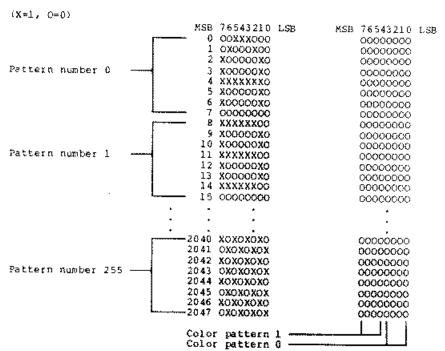

- 2. Pattern Generator Table Settings

- The pattern generator table is an area that stores the pattern fonts. Each pattern has a number from PNO to PN255.

- The font for each pattern is constructed from 8 bytes, and the lower two bits of each of the eight bytes is not displayed.

Set the beginning (head) address of the pattern generator table is

- register R#4.

|     | MSB | 7 | 6 | 5   | 4   | 3    | 2   | 1    | 0   | LB                                            |

|-----|-----|---|---|-----|-----|------|-----|------|-----|-----------------------------------------------|

| R#4 |     | 0 | a | A16 | A15 | Al 4 | Al3 | A1 2 | All | Pattern generator table base address register |

# Pattern generator table

(x=1, 0=0)

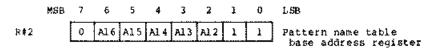

- Pattern name table settings

- The pattern name table is composed of one byte for each screen pattern. Each byte specifies a unique pattern.

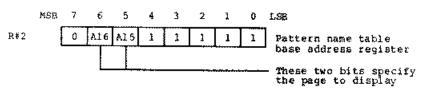

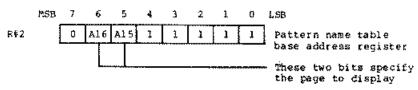

Set the beginning (head) address of the pattern name table in register R#2.

|     | MSB | 7 | 6   | 5   | 4    | 3   | 2    | 1   | 0    | LSB          |          |

|-----|-----|---|-----|-----|------|-----|------|-----|------|--------------|----------|

| R#2 |     | 0 | A16 | A15 | Al 4 | A13 | A1 2 | All | A1 0 | Pattern name | table    |

|     |     |   |     |     |      |     |      |     |      | base address | register |

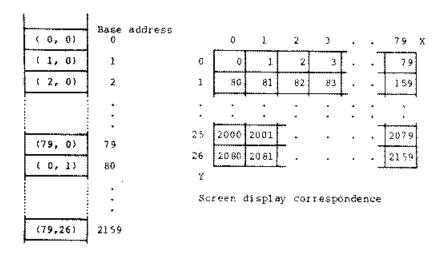

# Pattern name table

...

| (0,0)   | Base address<br>O |         | θ      | 1     | 2        | 3     |        |     | 39  |

|---------|-------------------|---------|--------|-------|----------|-------|--------|-----|-----|

| (1,0)   | 1 ^               | 8       | 0      | 1     | 2        | 3     | -      | ٠ T | 39  |

| ( 2, 0) | 2                 | 1       | 40     | 41    | 42       | 43    | ¯. ,   | • 1 | 79  |

|         | :                 | -       | :      | :     | :        | :     | -<br>: | :   | :   |

| (39, 0) | . 39              | 22      | 880    | 991   | <u>.</u> |       |        | -   | 919 |

| { 0, 1} | 40                | 23<br>¥ | 920    | 921   | - '      | •     | •      | · ] | 959 |

|         | :                 | Scr     | een di | splay | corr     | espor | idence | ė   |     |

| (39,23) | 959               |         |        |       |          |       |        |     |     |

# 4. Color register settings

Example of VRAM allocation in TEXT 1 mode

#### TEXT 2 MODE

#### Characteristics

- Pattern size : 6 dots (w) x 8 dots (h)

- Patterns : 256 types

- : BO (w) x 24 (h) patterns 80 (w) x 26.5 (h) patterns : Possible for each character - Screen pattern count - Pattern blinking

- Pattern colors : Two colors out of 512 colors (per screen),

- four if using blinking

- VRAM area per screen : 8K bytes

#### Controls

- Pattern font : VRAM pattern generator table

- Screen pattern location : VRAN pattern name table

- Blink attributes

- : VRAM color table : Bigh-order four bits of R#7 - Pattern color code 1 - Pattern color code 0 : Low-order four bits of R#7 - Background color code : Low-order four bits of R#7 - Pattern color code l : High-order four bits of R#12

- (Used for blinking) - Pattern color code 0 : Low-order four bits of R#12 (Used for blinking) . F.

Initial Settings

#### 1. Mode and Register Settings

|     | MSB | 7  | 6  | 5   | 4   | 3  | 2  | 1     | 0   | 82.1 |          |   |

|-----|-----|----|----|-----|-----|----|----|-------|-----|------|----------|---|

| R#0 |     | 0  | DG | IE2 | IEI | 0* | 1* | 0*    | 0   | Mode | register | 0 |

| R#1 |     | Đ  | BL | IE0 | 1*  | D* | 0  | នា    | MAG | Mode | register | 1 |

| R#B | :   | MS | LP | ŤP  | CB  | VR | 0  | SPD   | ₿W  | Mode | register | 2 |

| R#9 |     | LN | O  | 51  | S0  | ΙL | EQ | **141 | DC  | Mode | register | 3 |

- Examples of settings in TEXT 2 mode

- \*\* Indicates negative logic

In this display mode, if LN is set to 1, 26.5 lines are selected, and if LN is set to 0, 24 lines are selected.

- All other bits are set accordingly

#### 2. Pattern Generator Table Settings

- The pattern generator table is an area that stores the pattern fonts.

- Each pattern has a number from PNO to PN255.

- Set the beginning (head) address of the pattern generator table in register R#4.

|              | MSB | 7 | 6 | 5   | 4   | 3    | 2    | 1    | 0   | L5B                                              |

|--------------|-----|---|---|-----|-----|------|------|------|-----|--------------------------------------------------|

| ₽ <b>#</b> 4 |     | 0 | Û | A16 | Al5 | A1 4 | A) 3 | A1 2 | All | Pattern generator table<br>base address register |

- The fort for each pattern is constructed from 8 bytes, and the lower two bits of each of the eight bytes is not displayed.

Pattern generator table

(X≈1. O≈0)

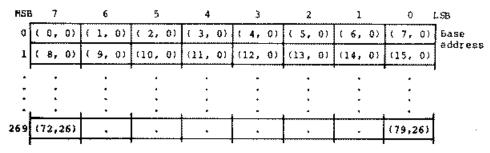

- 3. Pattern name table settings

- The pattern name table is composed of one byte for each screen pattern. Each byte specifies a unique pattern.

If LN is set to 0, the screen display pattern is 80 (w) x 24 (h); and if LN is set to 1, the screen display pattern is 80 (w) x 26.5 (h). The upper half of the 27th pattern (h) is displayed.

Set the beginning (head) address of the pattern name table in register R#2.

#### Fattern name table

#### 4. Color table settings

- In TEXT 2 mode, each pattern has a separate bit for the attribute area, and if this bit is set to 1, the pattern blink attribute will be set.

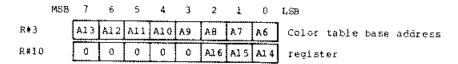

- Set the beginning (head) address of the color table in registers R#3 and R#10.

| MSB  | _7_ | 6    | 5   | 4    | 3  | 2 | ī   | 0 | LSB                    |

|------|-----|------|-----|------|----|---|-----|---|------------------------|

| R#3  | A13 | A1 2 | All | ALO. | P4 |   | ì   |   | Color table            |

| R#10 | 0   | 0    | 0   | 0    |    |   | A15 |   | base address registers |

# COLOR TABLE

- 5. Color register settings

- Set the color for pattern 1 in the high-order bits of register R#7. Set the color for pattern 0 in the low-order bits of register R#7.

|     | MSB | 7   |     | 5   | -   | _   | _   |     | -   | £SB             |      |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------------|------|

| ₽#7 |     | тсз | TC2 | TCl | TCO | BD3 | BD2 | BD1 | BD0 | Text color/Back | drop |

Set the blink attribute for the corresponding pattern by setting an alternate color code in register R#12. The pattern will be blinked by using the color codes set in registers R#7 and R#12.

|      | MSB | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   | LSB                            |

|------|-----|-------------|-----|-----|-----|-----|-----|-----|-----|--------------------------------|

| R#12 |     | <b>T2</b> 3 | T22 | T21 | T20 | всз | BC2 | BC1 | BCO | Text color/Back color register |

- 6. Blink register settings

- The color codes set in registers R#7 and R#12 will be alternately displayed for blinking; however, the blinking period attribute (time on and time off) can also be set in register R#13.

- The data for the ON and OFF times are shown below.(NTSC)

| DATA (Binary)                                                                                                                                                           | TIME (ms)                                                                                                                                                    | 1747                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 1 0 0 0 1 1 0 0 0 1 1 1 1 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0<br>166.9<br>333.8<br>500.6<br>667.5<br>834.4<br>1001.3<br>1168.2<br>1335.1<br>1501.9<br>1668.8<br>1835.7<br>2002.6<br>2169.5<br>2169.5<br>2336.3<br>2503.2 | 02000000000000000000000000000000000000 |

Example of VRAM allocation in TEXT 2 mode

MULTICOLOR MODE

#### Characteristics

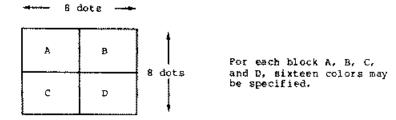

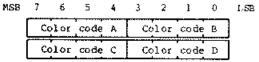

- Screen composition : 64 (w) x 48 (h) color blocks - Color blocks : Sixteen colors out of 512 colors - Sprite mode : Sprite mode 1

- Sprite mode : Sprite mode VRAM area per screen : 4K bytes

#### Controls

- Color block color code

- Color block location

- Background color code

- Sprites

- Sprites

- Color block location

- WRAM pattern mane table

- VRAM sprite attribute table

- VRAM sprite pattern table

# Initial Settings

1. Mode and Register Settings

|     | nsb | 7  | 6   | 5   | 4          | 3   | 2    | 1    | 0   | I.SB |          |   |

|-----|-----|----|-----|-----|------------|-----|------|------|-----|------|----------|---|

| R#0 |     | 0  | DG  | IE2 | IE1        | 0*  | 0*   | 0*   | Q   | Mode | register | 0 |

| R#1 |     | Ð  | BL. | IEO | p.e        | 1*  | 0    | SI   | MAG | Mode | reģister | 1 |

| R#8 |     | MS | ĹР  | TP  | CB         | VR  | 0    | SPD  | BW  | Mode | register | 2 |

| R#9 |     | LN | 0   | S1  | <b>S</b> 0 | IĻ, | EQ 3 | **%T | 20  | Mode | register | 3 |

- \* Examples of settings the display mode to the MULTICOLOR mode \*\* Indicates negative logic

- 2. Pattern Generator Table Settings

- The pattern generator table is an area that stores the colors of the color blocks.

- Each pattern is made up of four color blocks. These patterns are approximately 8 x 8 when the dots available for the screen display area is 256 x 192 dots.

- In the MULTICOLOR mode, two bytes are used for each pattern, and each pattern includes four color blocks.

In the MULTICOLOR mode, for each pattern name, there are four corresponding color blocks, and according to the y-coordinate, the pattern names are automatically set.

Set the beginning (head) address of the pattern generator table in register R#4.

Pattern generator table

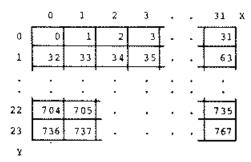

- 3. Pattern name table settings

- The pattern name table is composed of one byte for each screen pattern. Each byte specifies a unique pattern number.

Pattern name table

- Set the beginning (head) address of the pattern name table in register R#2.

Pattern name table

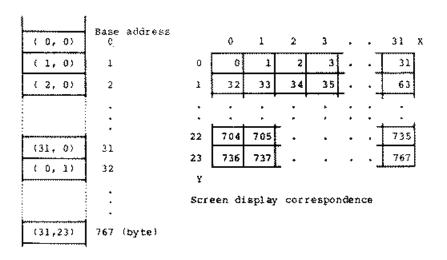

| (0,0)   | Base address<br>Q |

|---------|-------------------|

| (1,0)   | 1                 |

| (2, 0)  | 2                 |

|         | •                 |

| (31, 0) | 31                |

| (0,1)   | 32                |

|         | •                 |

| (31,23) | 767               |

# 4. Color register settings

# 5. Sprite settings

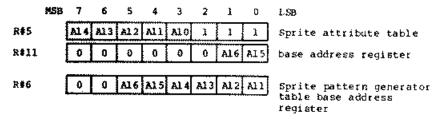

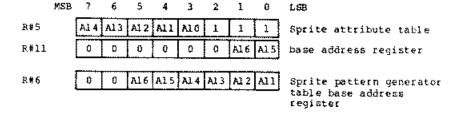

- Set the beginning (head) address of the sprite attribute table in registers R#5 and R#11; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details about sprites, see the section on SPRITE MODE 1.

|             | MSB | 7    | 6    | 5    | 4   | 3    | 2    | ì    | 8    | LSB                                                        |

|-------------|-----|------|------|------|-----|------|------|------|------|------------------------------------------------------------|

| R#5         |     | A1 4 | Al 3 | A1 2 | A11 | λld  | A9   | 8A   | Α7   | Sprite attribute table                                     |

| R#11        |     | 0    | 0    | 0    | 0   | 0    | 0    | A1 6 | A15  | base address register                                      |

| R <b>#6</b> |     | 0    | Ó    | A16  | A15 | Al 4 | A) 3 | AI 2 | Al l | Sprite pattern generator<br>table base address<br>register |

Example of VRAM allocation in MULTICOLOF mode

#### GRAPHIC 1 MODE

#### Characteristics

- : 8 dots (w) x 8 dots (h) : 256 types : 32 (w) x 24 (h) patterns : 16 colors out of 512 colors (per screen) : Sprite mode 1 - Pattern size - Patterns

- Screen pattern count Pattern colors Sprite mode

- Sprite mode

- VRAM area per screen : 4K bytes

#### Controls

- Pattern font : VRAM pattern generator table

- Screen pattern location : VRAM pattern name table

Pattern color codes 1 & 0 : Can be specified as a group for each

8-pattern set, in the VRAM color table

Background color code : Low-order four bits of R#7

Sprites : VRAM sprite attribute table, VRAM sprite

pattern table

# Initial Settings

# Mode and Register Settings

|     | MSB | 7  | 6  | 5    | 4          | 3   | 2  | 1    | Ð   | LSB  |          |   |

|-----|-----|----|----|------|------------|-----|----|------|-----|------|----------|---|

| ROO |     | ٥  | DG | 1 £2 | 181        | 0*  | 0* | 0*   | Ð   | Mode | register | Q |

| R#1 |     | 0  | BL | IEO  | g <b>*</b> | 0*  | 0  | SI   | MAG | Mode | register | 1 |

| R#8 |     | MS | LP | ΤP   | СВ         | VR  | 0  | SPÞ  | BW  | Mode | register | 2 |

| R#9 |     | LN | a  | Sl   | 50         | II. | EO | **NT | DC  | Mode | recister | 3 |

\* Examples of settings in GRAPHIC 1 mode \*\* Indicates negative logic

- 2. Pattern Generator Table Settings

- The pattern generator table is an area that stores the pattern fonts.

Each pattern has a number from PNO to PN255.

The font for each pattern is constructed from 8 bytes.

Set the beginning (head) address of the pattern generator table in register R#4.

|     | MSB | 7 | 6 | 5    | 4   | 3    | 2           | 1    | 0    | I-SB                                             |

|-----|-----|---|---|------|-----|------|-------------|------|------|--------------------------------------------------|

| R#4 |     | 0 | ٥ | A1 6 | A15 | λ1 4 | <b>Al</b> 3 | A1 2 | A1 1 | Pattern generator table<br>base address register |

#### Pattern generator table

#### (X=1, O=0)

- 3. Pattern name table settings

- The pattern name table is composed of one byte for each screen

- pattern. Each byte specifies a unique pattern.

Set the beginning (head) address of the pattern name table in register R#2.

|     | MSB | 7 | 6    | 5   | 4    | 3   | 2    | 1   | ũ    | t/SB                         |                   |

|-----|-----|---|------|-----|------|-----|------|-----|------|------------------------------|-------------------|

| R#2 |     | 0 | Al 6 | A15 | Al 4 | A13 | Al 2 | All | AJ 0 | Pattern name<br>base address | table<br>register |

#### Pattern name table

# 4. Color register settings

- 5. Color table settings

- The colors for pattern color 1 and pattern color 0 are set in groups

- of eight patterns.

Set the beginning (head) address of the color table in registers R#3 and R#10.

Color table

# Sprite settings

Set the beginning (head) address of the sprite attribute table in registers R#S and R#II; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details on sprites, see the section on SPRITE MODE 1.

|      | MSB | 7   | 6   | 5    | 4    | 3    | 2   | 1    | 0    | LSB                    |

|------|-----|-----|-----|------|------|------|-----|------|------|------------------------|

| R#5  |     | A14 | A13 | A1 2 | All  | A1 0 | A9  | 8A   | A7   | Sprite attribute table |

| R#11 |     | Q   | 0   | 0    | Ó    | Đ    | 0   | A16  | A1 5 | base address register  |

| R#6  | ļ   | Đ   | 0   | A16  | A1 5 | A1 4 | A13 | A1 2 | A11  | table base address     |

|      |     |     |     |      |      |      |     |      |      | register               |

\_\_\_\_\_\_

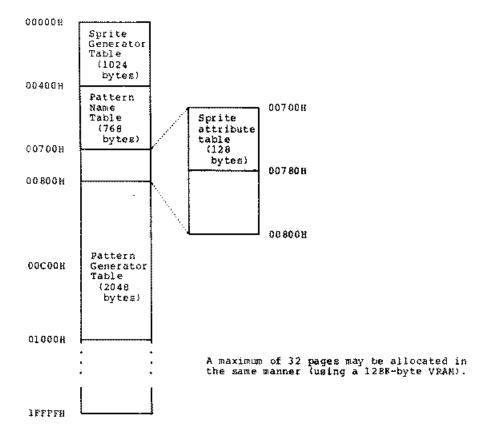

Example of VRAM allocation in GRAPHIC 1 mode

### GRAPHIC 2 AND GRAPHIC 3 MODES

### Characteristics

- Pattern size : 8 dots (w) x 8 dots (h)

- Patterns : 768 types

- Screen pattern count

- : 32 (w) x 24 (h) patterns : 16 colors out of 512 colors (per screen) : Sprite mode 1 (GRAPHIC 2) - Pattern colors

- Sprite modes Sprite mode 2 (GRAPHIC 3)

- VRAM area per screen : 16K bytes

- \* The GRAPHIC 2 and GRAPHIC 3 modes are identical except for the sprite modes.

### Controls

- Pattern font : VRAM pattern generator table

- Pattern font for vam pattern generator table vam pattern name table value for codes 1 s 0 : Can be specified as a group for each raster, in the VRAM color table sprites value table value table value table value table value table. pattern table

### Initial Settings

1. Mode and Register Settings

- \* Examples of settings in GRAPHIC 2 mode or GRAPHIC 3 mode \*\* Indicates negative logic All other bits are set accordingly.

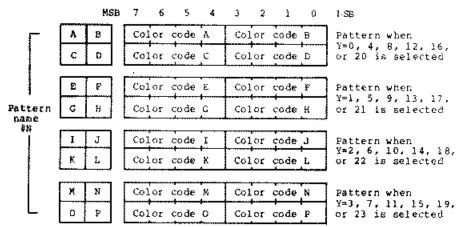

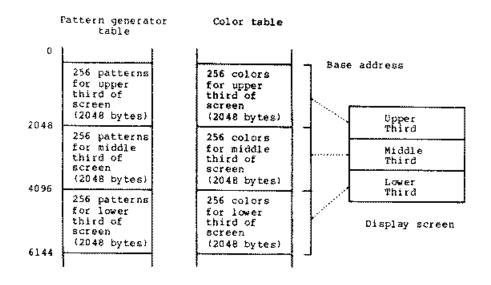

- 2. Pattern Generator Table Settings

- The pattern generator table is an area that stores the pattern fonts. Each pattern group has a number from PNO to PN255; and since each

- group may have three members, 768 patterns may be specified.

The font for each pattern is constructed from 8 bytes.

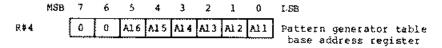

Set the beginning (head) address of the pattern generator table in register R#4.

|     | MSB | 7 | 6 | 5   | 4   | 3    | 2    | 1 | 0 | I:SB                                             |

|-----|-----|---|---|-----|-----|------|------|---|---|--------------------------------------------------|

| R#4 |     | 0 | 0 | A16 | A15 | A1 4 | A1 3 | 1 | 1 | Pattern generator table<br>base address register |

### 3. Color table settings

- The colors for pattern color 1 and pattern color 0 are set as a group of one raster.

- The color table corresponds to the pattern generator table on a oneto-one basis.

- Set the beginning (head) address of the color table in registers R#3 and R#10.

| 1    | MSB | 7   | 6 | 5 | 4 | 3 | 2 | 1   | Đ    | LSB                      |

|------|-----|-----|---|---|---|---|---|-----|------|--------------------------|

| R#3  |     | A13 | 1 | 1 | 1 |   | 1 | 1   | 1    | Color table base address |

| R#10 |     | 0   | 0 | 0 | Ò | 0 |   | A15 | A1 4 | register                 |

### 4. Color register settings

### Pattern generator table

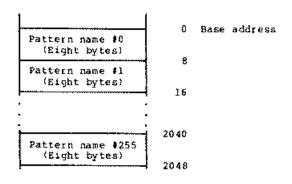

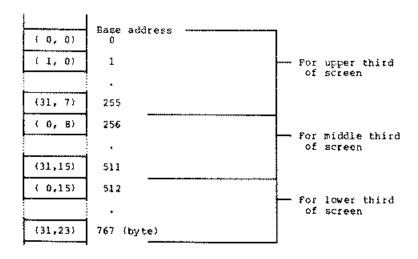

- Pattern name table sertings

- The pattern name table is composed of one byte for each screen pattern. Each byte specifies a unique pattern.

The upper, middle, and lower parts of the screen can be used as three different parts, for a total of 768 patterns.

# Pattern name table

| (0,0)   | Pattern display area for upper<br>third of screen (256 bytes) | (31, 0) |

|---------|---------------------------------------------------------------|---------|

| (0,7)   |                                                               | (31, 7) |

| (0,8)   | Pattern display area for middle                               | (31, 8) |

| ( 0,15) | third of screen (256 bytes)                                   | (31,15) |

| (0,16)  | Pattern display area for lower                                | (31,16) |

| (0,23)  | third of Screen (256 bytes)                                   | (31,23) |

- Set the beginning (head) address of the pattern name table in register R#2.

### Pattern name table

# 4. Sprite settings

- Set the beginning (head) address of the sprite attribute table in registers R#5 and R#11; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details about sprites pertaining to GRAPHIC 2 mode, see the section on SPRITE MODE 1, and for details about sprites pertaining to GRAPHIC 3 mode, see the section on SPRITE MODE 2.

|      | MSB | 7   | . 6 | 5   | 4   | 3    | 2    | 1    | Û    | LSB                                                        |

|------|-----|-----|-----|-----|-----|------|------|------|------|------------------------------------------------------------|

| R#5  |     | Al4 | A13 | A12 | A11 | A10  | A9   | A8   | A.7  | Sprite attribute table                                     |

| R#11 |     | 0   | Đ   | 0   | 0   | Ç.   | 0    | Al6  | A15  | base address register                                      |

| F.#6 |     | 6   | 0   | A16 | A15 | A1 4 | Al 3 | A1 2 | Al 1 | Sprite pattern generator<br>table base address<br>register |

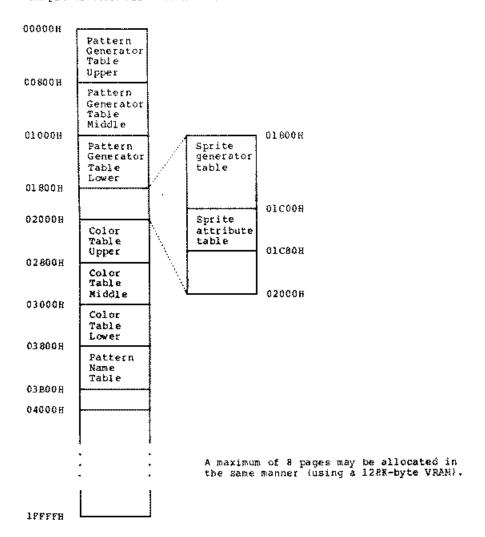

Example of VRAM allocation in GRAPHIC 2 mode

Example of VRAM allocation in GRAPHIC 3 mode

### GRAPHIC 4 MODE

### Characteristics

Initial Settings

. . . . .

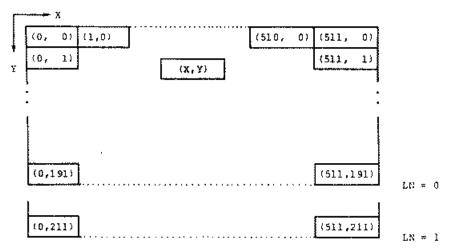

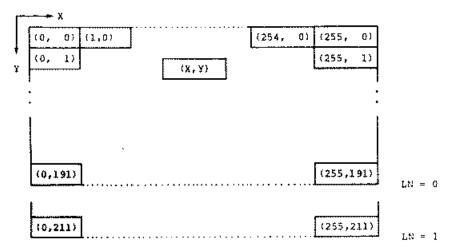

- Bit-mapped Graphics Mode Screen size

- : 256 (w) x 212 (h) dots 256 (w) x 192 (h) dots : 16 colors out of 512 colors (per screen) : Sprite mode 2 - Screen colors - Sprite mode

- VRAM area per screen : 32K bytes

### Controls

- Graphics : VRAM pattern name table

- Background color code - Sprites

- : Low-order four bits of R#7 : VRAM sprite attribute table, VRAM sprite pattern table

# 1. Mode and Register Settings

|     | MSB | 7  | 5  | \$  | 4   | 3  | 2   | 1   | 0   | Ł <i>S</i> B |          |   |

|-----|-----|----|----|-----|-----|----|-----|-----|-----|--------------|----------|---|

| £#0 |     | G  | DG |     | IEl |    | •   | 1 - | 0   | Mode         | register | 0 |

| R#1 |     | 6  | BL | ieo | 0*  | 0* | f _ | •   | MAG | Mode         | reçister | 1 |

| R#6 |     | MS | LP | TP  | CB  | VR | 0   | SPD | ₿₩  | Mode         | register | 2 |

| R#9 |     | ГN | 0  | \$1 | \$O | IL | EQ. | r/× | DÇ  | Mode         | reçister | 3 |

- \* Examples of settings in GRAPHIC 4 mode \*\* Indicates negative logic In GRAPHIC 4 mode, if LN is set to 1, the screen height is 212 dots, and if LN is set to 0, the screen height is 192 dots. All other bits are set accordingly.

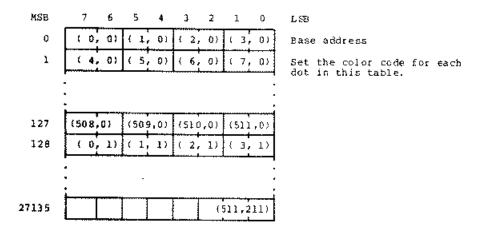

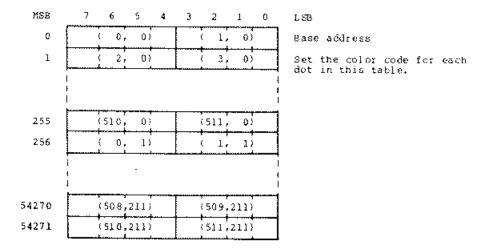

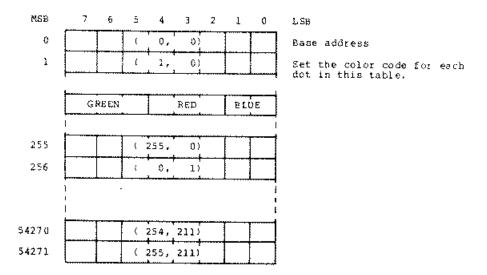

# 2. Pattern name table settings

The pattern name table is composed of one byte for every two dots on the screen. A color can be assigned for each dot from a selection of 16 colors out of 512 colors.

- Set the beginning (head) address of the pattern name table in register R#2.

### Pattern name table

| MSB   | 7           | 6    | 5    | 4 | 3 | 2    | 1           | 0 | L\$B                        |

|-------|-------------|------|------|---|---|------|-------------|---|-----------------------------|

| 1     |             | 0    | (1)  |   |   | 1,   | 0)          |   | Base address                |

| 2     |             | 2    | Q)   |   |   | 3,   | 0)          |   | Set the color code for each |

|       | •           |      |      |   |   |      |             |   | dot in this table.          |

|       | -<br>-<br>} |      |      |   |   |      |             | ; |                             |

| 127   |             | 254, | 0)   |   |   | 255  | 0)          |   |                             |

| 128   |             | ( 0, | 1)   |   |   | 1,   | 1)          |   |                             |

|       |             |      | •    |   |   |      | <del></del> |   |                             |

| ·     |             |      |      |   |   |      |             | : |                             |

| 27134 |             | 252, | 211} |   |   | 253, | 211)        |   |                             |

| 27135 |             | 254, | 231) |   |   | 255, | 211)        |   |                             |

# 3. Color register settings

### 4. Sprite settings

Set the beginning (head) address of the sprite attribute table in registers R#5 and R#11; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details about sprites, see the section on SPRITE MODE 2.

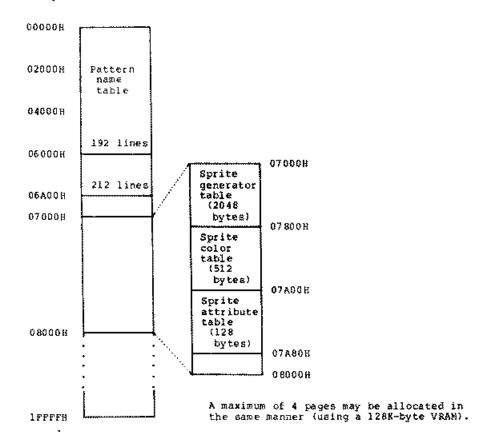

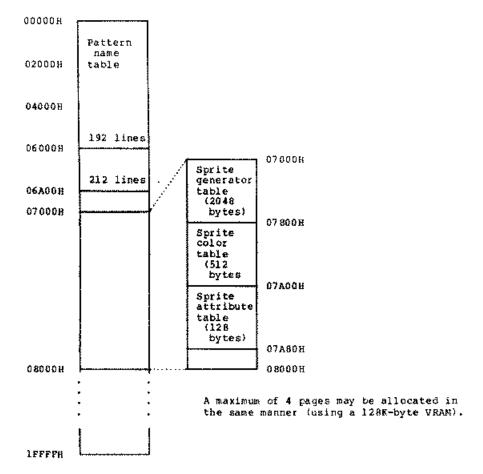

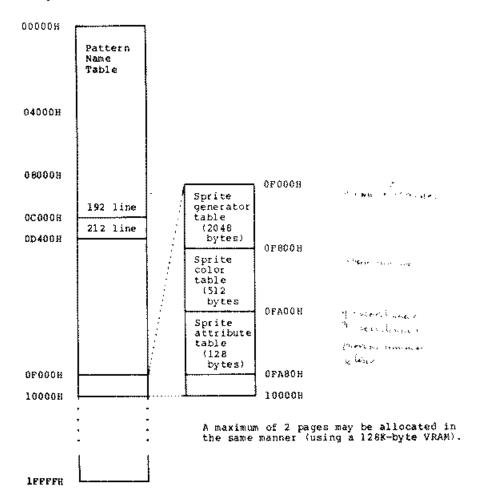

Example of VRAM allocation in GRAPHIC 4 mode

### GRAPHIC 5 MODE

### Characteristics

- Bit-mapped Graphics Mode

- Screen size

- : 512 (w) x 212 (h) dots 512 (w) x 192 (h) dots : 4 colors out of 512 colors (per screen) : Sprite mode 2

- Screen colors Sprite mode VRAM area per screen

- : 32K bytes

### Controls

- Graphics

- Background color code

- : VRAM pattern name table : Low-order four bits of R#7 : VRAM sprite attribute table, VRAM sprite pattern table - Sprites

### Initial Settings

### 1. Mode and Register Settings

|     | MSB | 7  | 6  | 5   | 4   | 3  | 2  | 1   | 0   | LSB  |          |   |

|-----|-----|----|----|-----|-----|----|----|-----|-----|------|----------|---|

| R#0 |     | G  | DG | 1E2 | IEI | 1* | 0. | 0*  | a   | Mode | register | 0 |

| R#1 |     | 0  | BL | 1E0 | 0*  | 0* | 0  | sī  | MAG | Mode | register | 1 |

| R#8 |     | MS | LP | TP  | СВ  | VR | Û  | SPD | BW  | Hode | register | 2 |

| R#9 |     | LN | 0  | Ş1  | SÖ  | IL | ΕO | *NT | DC. | Mode | register | 3 |

- \* Examples of settings in GRAPHIC 5 mode \*\* Indicates negative logic In GRAPHIC 5 mode, if LN is set to 1, the screen height is 212 dots, and if LN is set to 0, the screen height is 192 dots. All other bits are set accordingly.

- 2. Pattern name table settings

- The pattern name table is composed of one byte for every four dots on the screen. A color can be assigned for each not from a selection of 4 colors out of 512 colors.

- Set the beginning (head) address of the pattern name table in register R#2.

Pattern name table

### 3. Color register settings

### 4. Sprite settings

Set the beginning (head) address of the sprite attribute table in registers R#5 and R#11; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details about sprites, see the section on SPRITE MODE 2.

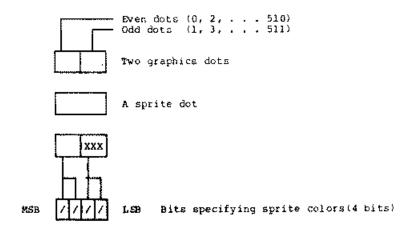

5. Hardware tiling function

......

- In GRAPHIC 5 mode, a hardware tiling function processes the sprite In GRAPHIC 5 mode, a hardware tiling function processes the sprite and background colors. For these colors, you can specify four bits; however, of these four bits, the higher-order two bits specify the color code of the even dots, and the lower-order two bits specify the color code of the odd dots of the x-coordinate (0 to 511).

In GRAPHIC 5 mode, the size of one dot of a sprite is approximately twice that of a graphics dot; however, when this tiling function is used, one dot of a sprite may be displayed in two colors.

The even and odd dots of the background color may also be specified in the same manner.

- in the same manner.

Example of VRAM allocation in GRAPHIC 5 mode

### CRAPHIC 6 MODE

### Characteristics

- Bit-mapped Graphics Mode

- Screen size

- : 512 (w) x 212 (h) dots 512 (w) x 192 (h) dots : 16 colors out of 512 colors (per screen) : Sprite mode 2 : 128K bytes (Two screens) - Screen colors

- Sprite mode

- VRAM area per screen

- \* To use this mode, the VRAM must have 128K bytes.

### Controls

- : VRAM pattern name table - Graphics

- : Low-order four bits of R#7 - Background color code : VRAM sprite attribute table, VRAM sprite pattern table - Sprites

### Initial Settings

# Mode and Register Settings

|     | MSB | 7  | 6  | 5   | 4   | 3   | 2  | 1    | 0   | LSB<br>- |          |   |

|-----|-----|----|----|-----|-----|-----|----|------|-----|----------|----------|---|

| R#0 |     | Ģ  | DG | 1E2 | ïEl | 1*  | 0* | 1*   | 0   | Mode     | register | Ó |

| R#1 |     | 0  | BL | 1E0 | 0*  | 0*  | 0  | sī   | MAG | Mode     | register | 1 |

| R#8 |     | HS | LP | TP  | СB  | VR  | 0  | SPD  | BW  | Mode     | register | 2 |

| R#9 |     | LN | To | Sl  | so  | 11L | EO | **NT | DC  | Mode     | register | 3 |

\* Examples of settings in GRAPHIC 6 mode \*\* Indicates negative logic In GRAPHIC 6 mode, if IN is set to 1, the screen height is 212 dots, and if IN is set to 0, the screen height is 192 dots. All other bits are set accordingly.

or oppositional assessment to the control of the co

- 2. Pattern name table settings

- The pattern name table is composed of one byte for every two dots on the screen. A color can be assigned for each dot from a selection of 16 colors out of 512 colors.

Set the beginning (head) address of the pattern name table in register R#2.

Pattern name table

### 3. Color register settings

### 4. Sprite settings

Set the beginning (head) address of the sprite attribute table in registers R#5 and R#11; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details about sprites, see the section on SPRITE MODE 2.

Example of VRAM allocation in GRAPHIC 6 mode

### GRAPHIC 7 MODE

# Characteristics

- Bit-mapped Graphics Mode

- Screen size : 256 (w) x 212 (h) dots 256 (w) x 192 (h) dots

- Screen colors Sprite mode VRAM area per screen

- : 255 colors (per screen) : Sprite mode 2 : 128K bytes (Two screens)

- \* To use this mode, the VRAM must have 128K bytes.

### Controls

- Graphics

- : VRAM pattern name table

- Sackground color code Sprites : Low-order four bits of R#7 : VRAM sprite attribute table, VRAM sprite

pattern table

### Initial Settings

# 1. Mode and Register Settings

|     | MSB | 7  | - 6 | 5   | 4   | 3   | 2  | 1   | 0   | LSB. |          |   |

|-----|-----|----|-----|-----|-----|-----|----|-----|-----|------|----------|---|

| R#0 |     | 0  | ĎĢ  | 162 | IEI | 1*  | 1* | 1*  | 0   | Kođe | register | 0 |

| R#1 |     | 0  | BL. | 1E0 | 0*  | 0*  | D  | Sī  | MAG | Mode | register | 1 |

| R#8 |     | MS | LP  | TP  | СВ  | VR  | 0  | SPD | B₩  | ×oαe | register | 2 |

| R#9 |     | LN | Đ   | Sl  | so  | 11. | EC | *NT | DÇ  | Mode | register | 3 |

- \* Examples of settings in GRAPHIC 7 mode

- \*\* Indicates negative logic

In GRAPHIC 7 mode, if LN is set to 1, the screen height is 212 dots, and if LN is set to 0, the screen height is 192 dots. All other bits are set accordingly.

- 2. Pattern name table settings

- The pattern name table is composed of one byte for every dot on the screen. A color can be assigned for each dot from a selection of 256 colors.

- Set the beginning (head) address of the pattern name table in register R\*2.

Creen Ista I sive

V9938 MSX-VIDEO USER'S MANUAL

Pattern name table

3. Color register settings

# 4. Sprite settings

- Set the beginning (head) address of the sprite attribute table in registers R#5 and R#11; and set the beginning (head) address of the sprite pattern generator table in register R#6. For details about sprites, see the section on SPRITE MODE 2.

|      | MSB | . 7  | 6   | 5    | 4    | 3    | 2   | 1    | 0    | LSB                            |

|------|-----|------|-----|------|------|------|-----|------|------|--------------------------------|

| R#5  |     | A1 4 | A13 | Al 2 | Al I | Al 0 | 1   | 1    | 1    | Sprite attribute table         |

| R#11 |     | 0    | 0   | 0    | 0    | 0    | ō   | Al6  | A15  | base address register          |

| R#6  |     | 0    | ٥   | A16  | A15  | A1 4 | A13 | Al 2 | Al l | Sprite pattern generator       |

|      |     |      |     |      |      |      |     |      |      | table base address<br>register |

Example of VRAM allocation in GRAPHIC 7 mode

### COMMANDS

# 1. Types of Commands

It is very easy to use MSX-VIDEO commands to perform functions such as LINE and PSET for use with graphics, and for transferring parts of the screen.

Summary of Commends

| Command Name       | Destination  | Sour ce      | Late         | Mnemonic     | CM3 | CM2 | CMI | CMD |

|--------------------|--------------|--------------|--------------|--------------|-----|-----|-----|-----|

| Righ-speed         | VRAN<br>VRAN | CPU<br>VRAN  | Byte<br>Byte | HMMC<br>YMMM | 1   | 1   | 1   | 1   |

|                    | VRAM<br>VRAM | VRAM         | Bŷte         | HMMH         | 1   | i   | ō   | 0   |

| Logical move       | VRAN         | V DP<br>CPU  | Byte<br>fot  | LMMC         | 1   | 1 0 | 1   | 0   |

|                    | CPU<br>VRAM  | VRAN<br>VRAN | Dot          | LMCM<br>LMMM | 1   | ¢   | î   | ç   |

| Line               | VRAM<br>VRAM | VDP          | Dot          | LMMV         | i   | 0   | 0   | Ô   |

| Search             | VRAM         | VDP<br>VDP   | Dot          | LINE         | 0   | 1   | 1   | 1   |

| Pset<br>Point      | VRAM<br>VDP  | VDP<br>VRAM  | Dot          | PSET         | 0   | ï   | ō   | ì   |

| Invalid<br>Invalid | 1            | 1            | ]            | TOIN!        | 0   | 0   | 1   | 1   |

| Invalid            |              |              |              |              | 0   | 0   | 1 0 | 0   |

| Stop               | ļ            |              | -            |              | 0   | ō   | ō   | ō   |

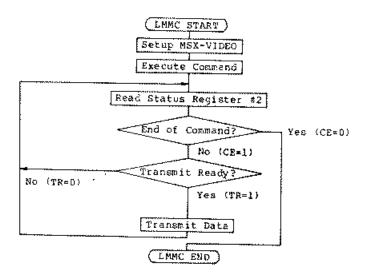

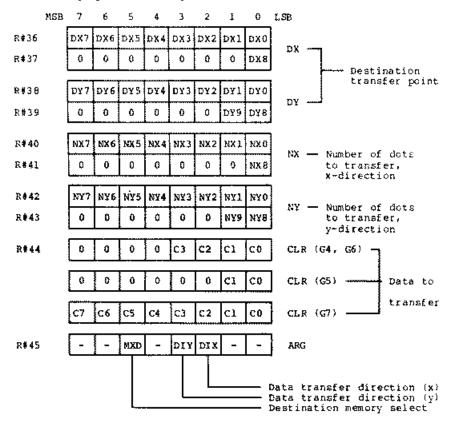

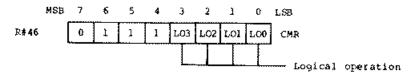

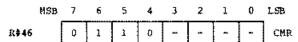

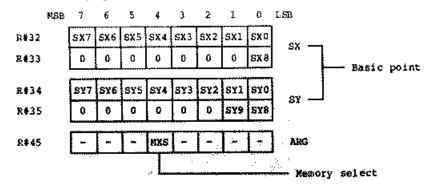

Commands are executed in the MSX-VIDEO by writing the data into R#46 (the Command Register, hereafter abbreviated CMR), and setting bit 0 of status register S#2 (CE/Command Execute) to 1. Before this can be done, the necessary parameters must be first have been set in registers R#32 to R#45.

When the command execution is complete, CE is set to 0.

To abort a command while it is being executed, execute a STOP.

The results of command execution are only guaranteed during bit map mode (Graph4 to Graph7).

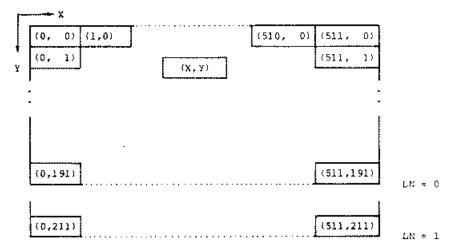

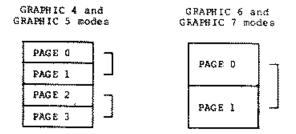

### 2. Page Concept

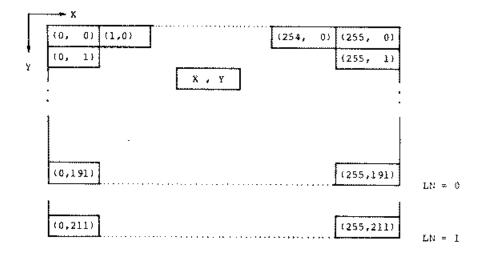

The parameters used for the MSX-VIDEO are all x-y coordinates. In other words, the internal command processor of the MSX-VIDEO accesses the entire VRAM area as x-y coordinates of the display mode.

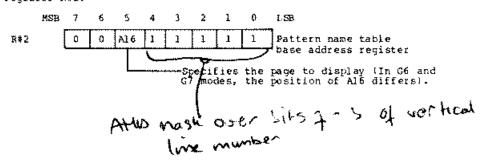

When a screen is to be displayed, 212 lines of the same page are displayed (selected by  $R \neq 23$ ). To select the page to be displayed, use  $R \neq 2$ .

When a command is being executed, the contents of the display screen are ignored.

The display modes and their relationships to the coordinates are shown in the table below.

GRAPH 4 Address GRAPH 5 H00000 (0,0) (255,0) (0,0) (511,0)Page 0 Page 0 (0,255) (0,255) (511,255) (255,255) H 0 0 0 9 0 (0,256) (255,256) (0.256)(511,256) Page 1 Page 1 (0,511) (255,511) (0,511) (511,511) 10000H (0,512) (255,512) (0,512)(511,512) Page 2 Page 2 (0,767) (0,767) (255,767) (511,767) 18000# (511,76B) (0,768)(255,768) (0.768)Page 3 Page 3 (0,1023) (511,1023) (0,1023) (255,1023) 1FFFFH

| GRAZII  | •    |           |                     |

|---------|------|-----------|---------------------|

| (0,0)   | *    | {255,0}   | 00000н              |

| (0,255) | Page | (255,255) | 10000H              |

| (0,256) |      | (255,256) | 100001              |

| (0,511) | Page | (255,511) | <br>1 <b>5</b> 7758 |

|         |      |           | 76666               |

CORDS 7

| <u></u> |                     |

|---------|---------------------|

| (0,0)   | (511,0)             |

| (0,255) | Page 0 (511,255)    |

| (0,256) | (511,256)           |

| (0,511) | Page 1<br>(511,511) |

GRAPH 6

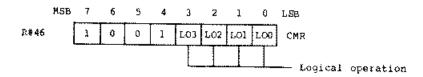

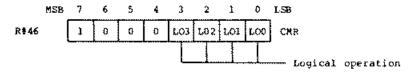

# 3. Logical Operations

When the LINE, PSET, and LOGICAL MOVE commands are executed on the MSX-VIDEO, the operations may be performed on the color on the screen. To do logical operations on the MSX-VIDEO, write the lower four bits of R#46 (Command register) simultaneously when you specify the command.

Summary of Logical Operations

<sup>\*</sup> SC = Source Color code \* DC = Destination Color code \* EOR = Exclusive OR

- 4. Explanations of Commands

- 4.1 HMMC (High-speed move CPU to VRAM)

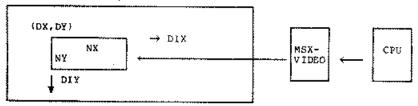

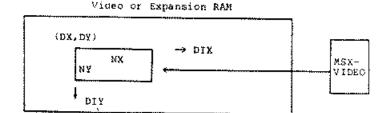

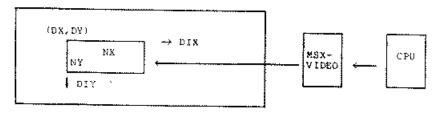

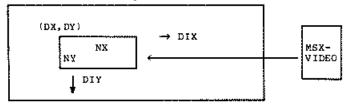

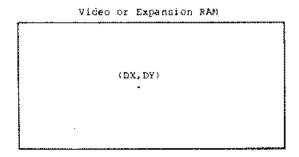

The HMMC command transfers data from the CPU to the Video or expansion RAM in a specified rectangular area (in x-y coordinates) via the MSX-VIDEO.

Since the data to be transferred is done in units of one byte, there is a limitation, according to the display mode, on the value for x.

Video or Expansion RAM

### 4.1.1 HMMC Execution Order

First, set the necessary parameters in the command register of the MSX-VIDEO.

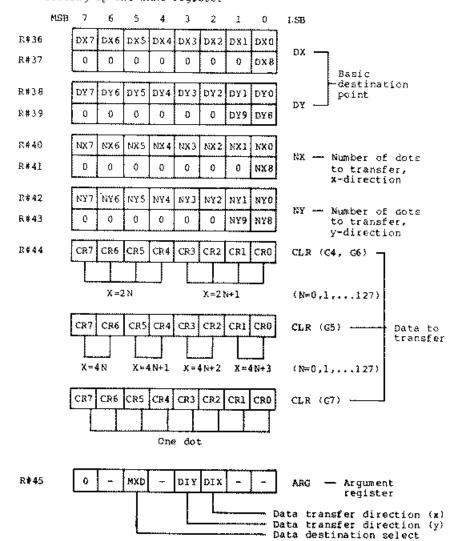

MXD: Select destination memory

0: Video RAM 1: Expansion RAM

DX: Basic x-coordinate of destination (0 to 511) \*I

DY: Basic y-coordinate of destination (0 to 1023)

NX: Dots to move in x-direction (0 to 511) \*1

NY: Dots to move in y-direction (G to 1023)

\*1 Note that in the G4 and G6 modes, the lower one bit, and in the G5 mode, the lower two bits, are lost.

DIX: Direction for NX from x-coordinate of destination

0: Right l: Left

DIY: Direction for NY from y-coordinate of destination 0: Down 1: Up

CLR (R#44:Color register):

First byte of data to be transferred

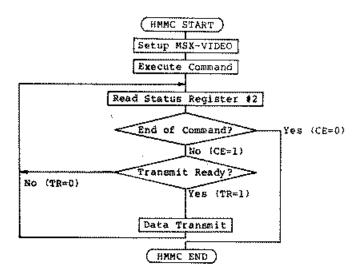

- After you specify the above data, execute the command by writing 1 1 1 1 0 0 0 0 B into the CMR(R#46:Command register).

- 3. While checking TR and CE in Status Register S#2, send the second byte and all bytes following into the CLR register.

### 4.1.2 Setting up the HMMC register

### 4.1.3 Execution of HMMC commands

| MSB  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | LSB |

|------|---|---|---|---|---|---|---|---|-----|

| R#46 | ī | 1 | 1 | 1 | - |   | - | _ | ÇMR |

# 4.1.4 Flowchart of HMMC execution

4.2 YMMM (High-speed move VRAM to VRAM, y only)

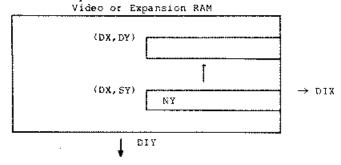

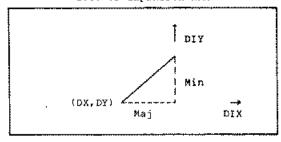

The YMMM command transfers data from the area specified by DX, SY, NY, DIX, DIY and the right (or left) edge of the Video RAM, in the ydirection determined by DY.

### 4.2.1 YMMM Execution Order

- Pirst, set the necessary parameters in the command register of the MSX-VIDEO.

- MXD: Select destination memory

- 0: Video RAM 1: Expansion RAN

- DY: Basic y-coordinate of destination (0 to 1023)

- Basic x-coordinate of source point (0 to 511) \*1

Basic y-coordinate of source point (0 to 1023)

- SX:

- Dots to move in y-direction (0 to 1023)

- \*1 Note that in the G4 and G6 modes, the lower one bit, and in the G5 mode, the lower two bits, are lost.

- DIX: Direction for x-coordinate of source point to the right or left end of screen

- 0: Right 1: Left

- DIY: Direction of source point from NY

- 0: Down 1: Up

- 2. After you specify the above data, execute the command by writing 1 I I I 0 0 0 0 B into the CMR(R\*46:Command register).

- The above procedure will execute the YMMM command in the MSX-VIDEO. While executing the YMMM command, the CE bit of the status register (S $\sharp$ 2) will be set to 1, and when the command is complete, it will be reset to 0.

# 4.2.2 Setting up the YMMM register

### 4.2.3 Execution of YMMM Commands

.· ····· ·· :

### 4.3 HMMM (High-speed move VRAM to VRAM)

The HMMM command transfers data in a specified rectangular area from the VRAM or the expansion RAM,  ${\sf VRAM}$  or the expansion RAM,

Since the data to be transferred is done in units of one byte, there is a limitation, according to the display mode, on the value for x.

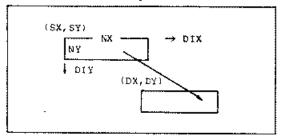

(SX, SY) NX · → DIX ΝY DIY (DX, DY)

Video or Expansion RAM

### 4.3.1 HMMM Execution Order

- 1. First, set the necessary parameters in the command register of the MSX-VIDEO.

- Select source memory 0: Video RAM MXS:

- 1: Expansion RAM

- Select destination memory 0: Video RAM MXD :

- 0: Video km. 1: Expansion RAM

- SX: Source point x-coordinate (0 to 511) \*1

- SY: Source point y-coordinate (0 to 1023)

- Dots to move in x-direction (0 to 511) \*1 NK:

- Dots to move in y-direction (0 to 1023) NY:

- Direction for NX from source point DIX:

- 0: Right 1: Left

- DIY; Direction for NY from source point

- 0: Down

- 1: 0p

- DX: Basic x-coordinate of destination (0 to 511) \*1 Basic y-coordinate of destination (0 to 1023)

- DY:

- \*1 Note that in the G4 and G6 modes, the lower one bit, and in the G5 mode, the lower two bits of SX, DX, and NX, are lost.

- 2. After you specify the above data, execute the command by writing 1 1 0 1 0 0 0 0 m into the CMR(R#46:Command register).

3. The above procedure will execute the HMMM command in the MSX-VIDEO. While executing the HMMM command, the CE bit of the status register  $\{\$42\}$  will be set to 1, and when the command is complete, it will be reset to 0.

### 4.3.2 Setting up the HMMM register

### 4.3.3 Executing the HMMM command

|      | MSB | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | LSB |

|------|-----|---|---|---|---|---|---|---|---|-----|

| R#46 |     | 1 | 1 | Ð | ļ |   | - | _ | - | CMR |

4.4 HMMV (High-speed move VDP to VRAM)

The HMMV command is used to paint in a specified rectangular area of the VRAM or the expansion RAM.

Since the data to be transferred is done in units of one byte, there is a limitation, according to the display mode, on the value for x.

# 4.4.1 HMMV Execution Order

Pirst, set the necessary parameters in the command register of the MSX-VIDEO.

MXD: Select destination memory

0: Video RAM 1: Expansion RAM

Dots to move in x-direction (0 to 511) \*1 Dots to move in y-direction (0 to 1023) KX:

NY:

DIX: Direction for NX from source point

0: Right 1: Left

Direction for NY from source point DIY:

0: Down 1: Up

DX: Basic x-coordinate of destination (0 to 511) \*1 Basic y-coordinate of destination (0 to 1023)

\*1 Note that in the G4 and G6 modes, the lower ore bit, and in the G5 mode, the lower two bits of DX and NX, are lost.

CLR: Color code data

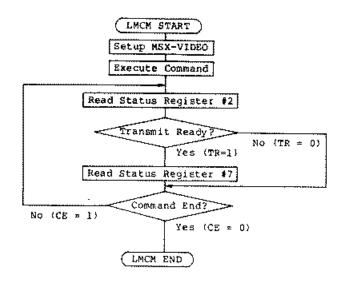

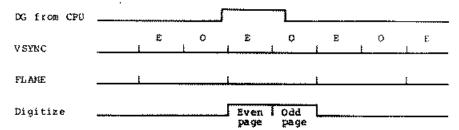

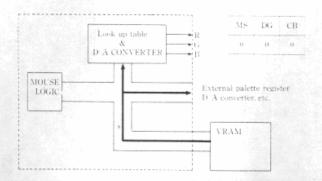

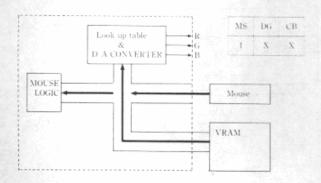

- After you specify the above data, execute the command by writing 1 1 0 0 0 0 0 0 into the CMR.